# Implementation of UART using Verilog HDL and FPGA

Ms. Aruna Dore<sup>1</sup>, K.H.N.M.Ramakrishna<sup>2</sup>, L.Premanandareddy<sup>3</sup>, Vageesh A<sup>4</sup>, Pritham Ashok Rudrapur<sup>5</sup>

<sup>1</sup>Assistant Professor, Electronics and Communication Engineering, Presidency University

<sup>2</sup>Student, Electronics and Communication Engineering, Presidency University

<sup>3</sup>Student, Electronics and Communication Engineering, Presidency University

<sup>4</sup>Student, Electronics and Communication Engineering, Presidency University

#### Abstract -

This study presents a hardware-based implementation of Universal Asynchronous Receiver Transmitter (UART) communication on the Nexys A7-100T Field Programmable Gate Array (FPGA) platform using Verilog HDL and Vivado Design Suite. UART serves as a fundamental serial communication protocol, widely adopted due to its simplicity and effectiveness. The work details the design methodology, including clock division, baud rate generation, and serial data transmission, while demonstrating successful communication between FPGA and PC. Experimental results confirm reliable and low-power serial data exchange, making this implementation ideal for embedded and communication systems.

#### Keywords

UART, FPGA, Serial Communication, Verilog HDL, Nexys A7-100T, Vivado, VLSI, Clock Gating

# **1.INTRODUCTION**

Serial communication protocols such as UART are pivotal in embedded systems where resource-efficient and reliable data exchange is essential. Unlike parallel transmission, UART utilizes a minimal number of data lines, making it highly suitable for FPGA-based systems. This paper focuses on the design and implementation of UART protocol on the Digilent Nexys A7-100T FPGA board using Xilinx Vivado and Verilog HDL. The approach aims to minimize hardware complexity while ensuring communication accuracy and power efficiency.

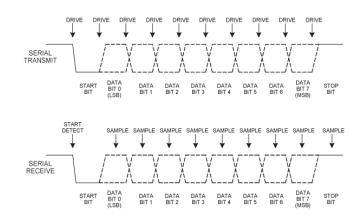

# **1.1 UART** frame format for both transmitter and receiver

The design incorporates a UART receiver module, enabling secure communication with the processor and facilitating the exchange of authentication keys through a terminal interface, such as PuTTY.Authentication keys fetched via UART are validated by the processor's security mechanisms before granting access to its core functionalities

# 2. Related Work

Several studies have explored UART protocol implementations using FPGAs. Prior work has emphasized baud rate accuracy, synchronization challenges, and resource optimization. This study builds upon these efforts by integrating clock gating techniques for power reduction and by validating the system using hardware-level testing between the FPGA board and a computer terminal.

# 3. Methodology

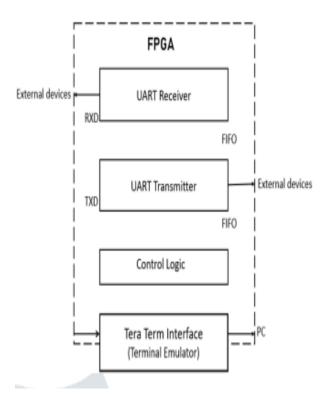

The design follows a modular structure comprising:

• **Baud Rate Generator**: Divides the system clock to match the UART baud rate.

• **Transmitter (TX) Module**: Converts parallel data to serial for output.

• **Receiver** (**RX**) **Module**: Captures and reconstructs incoming serial data.

• **Clock Gating**: Employed to reduce dynamic power consumption in idle states.

# **Basic Features of UART Communication:**

#### Asynchronous Communication.

**Full Duplex:** Simultaneous data transmission and reception.

**Baud Rate:** Defines the speed of communication (e.g., 9600, 19200).

**Start and Stop Bits:** Used to identify the beginning and end of data.

Parity Bit: Optional error checking mechanism.

**Data Frame:** Usually 8-bit data, but configurable depending on application.

# 4. Implementation

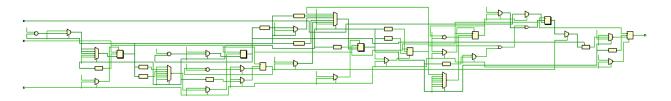

The system was developed using Verilog HDL in the Vivado 2024.1 suite. Simulation was conducted using Vivado's built-in testbench environment to verify timing, bit accuracy, and module interaction. The design was synthesized and deployed onto the Nexys A7-100T FPGA, and connected to a PC through a USB-UART interface. Data exchange was monitored via a serial terminal program. Advantages

Reliable performance Compatibility with most systems. Scalability. Flexibility Real-Time Monitoring with Putty

# Limitations

Not suitable for long distances or very high speeds. No default support for addressing multiple devices (unlike I2C).

Sensitive to baud rate mismatch.

# 5. Results and Discussion

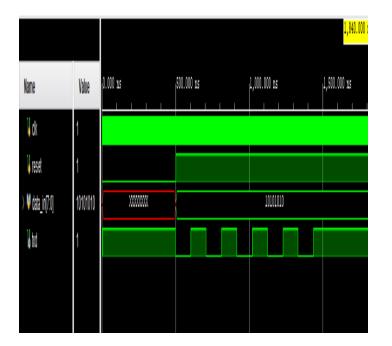

The UART modules performed accurately at a baud rate of 9600 bps. Timing analysis confirmed compliance with UART communication standards. The power consumption was observed to reduce significantly when clock gating was active. Resource utilization (LUTs, Flip-Flops, etc.) remained within efficient limits, indicating scalability for larger embedded system.

# Architecture Diagram

I

Fig1:- UART - Simulation Waveform

# Hardware Interfacing and Testing with PuTTY

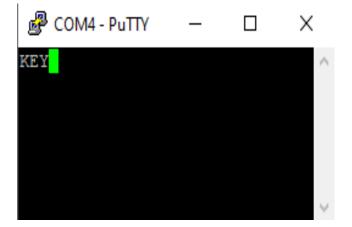

To validate the UART module implemented using Verilog HDL, the design was synthesized and programmed onto the Nexys A7-100T FPGA board using Xilinx Vivado. Real-time serial communication was tested through the **PuTTY terminal**, a widely used serial communication tool.

# **Connecting with PuTTY**

Open PuTTY and select Serial as the connection type.

Set the COM port detected by your USB-to-UART (you can find it in Device Manager on Windows).

Set Baud rate to 19200, Data bits to 8, Stop bits

to 1, Parity to None, and Flow control to None..

#### Procedure

Load the bitstream onto the Nexys A7 via • Vivado.

• Open PuTTY and press the reset button on the board.

Use the DIP switches to set an 8-bit value. •

Observe the corresponding character appear on the PuTTY terminal

#### Verification

0

0

0

The testbench was verified using simulation, and hardware functionality was validated by checking:

Correct character display on PuTTY.

Real-time transmission at the set baud rate.

Stability across multiple transmissions.

Fig4: o/p Terminal

Fig5: inputs (ASCII values)

# Character ASCII (Decimal) ASCII (Hex) ASCII (Binary)

| k | 107 | 0x6B | 01101011 |

|---|-----|------|----------|

| e | 101 | 0x65 | 01100101 |

| У | 121 | 0x79 | 01111001 |

**ASCII** values for K,E,Y

SJIF Rating: 8.586

ISSN: 2582-3930

## 6. Conclusion

this In project. а Universal Asynchronous Receiver/Transmitter (UART) communication protocol was successfully designed and implemented using Verilog HDL, with real-time validation carried out on an FPGA platform. The system was composed of two key modules: a transmitter for converting parallel data into serial form with proper framing, and a receiver for capturing the serial data, verifying its integrity, and converting it back to parallel form. A baud rate generator operating at a predefined speed of 19200 baud ensured accurate timing and synchronization between the transmitter and receiver, enabling reliable data transmission. This work demonstrates a reliable and lowpower UART implementation on an FPGA platform. Through modular design and clock gating, the system balances performance with energy efficiency. The design suitable for integration into broader SoC is communication systems, with potential for further expansion into high-speed or multi-UART architectures.

#### REFERENCES

Biswajit Roy Dakua, Md. Ismail Hossain and Foisal Ahmed "Design and Implementation 1. of UART Serial Communication Module Based on FPGA" June 2015 DOI:10.5281/zenodo.7419148

2. Pavithra L., A STUDY ON SMART HOME INTEGRATION WITH FPGA CONTROLLER, IJRE - International Journal of Research in Electronics Volume: 06 Issue: 01 2019.

3. P. Bhargav Ram1, B. Uday Kiran2, M. Prashanth Nayak3 "FPGA Implementation of Gesture based Home Automation" INTERNATIONAL JOURNAL OF SCIENTIFIC PROGRESS AND RESEARCH (IJSPR) ISSN: 2349-4689 Issue 173, Volume 73, Number 01, July 2020

4. Kavyashree S, "Design and Implementation of UART using Verilog", International Journal Of Engineering And Computer Science ISSN:2319-7242 Volume - 4 Issue - 12 December, 2015

5. Abhay Malviya, Vijay Kumar Sharma, "An Improved Approach of UART Implementation in VHDL using Status Register", Volume 4, Issue 10, May 2016 International Journal of Digital Application & Contemporary ResearchL.

Larsson, A. Killingworth, K.Lagemann, —Teaching System Integration using FPGA [6] 6. Ravi Payal; Akanksha Saxena; Beena Chanda,"Implementation of Smart Home through FPGA using Verilog Hardware Descriptive Language" 2020 IEEE International Conference on Advent Trends in Multidisciplinary Research and Innovation

7. Umakanta Nanda, Sushant Kumar Pattnaik, "Universal Asynchronous Receiver and Transmitter(UART)", 2016 3rd International Conference on Advanced Computing and Communication Systems (ICACCS -2016), Jan. 22 – 23, 2016, Coimbatore

I