# IC Design for IOT Devices with Low Cost, Compact Size, and Minimal Power Consumption

# <sup>1</sup> M.L. Sharma, <sup>2</sup>S S Deswal, <sup>3</sup>Sunil Kr. Mathur, <sup>4</sup>Aniket Pal, <sup>5</sup>Ansh Gupta

1,2,3 Professor, Maharaja Agrasen Institute of Technology, Delhi

<sup>4,5</sup>Research Scholar, Electronics and Communication Department, Maharaja Agrasen Institute of Technology, Delhi

<sup>1</sup>mlsharma@mait.ac.in, <sup>2</sup>satvirdeswal@hotmail.com, <sup>3</sup>sunilkumar@mait.ac.in, <sup>4</sup>aniketpal752@gmail.com, <sup>5</sup>anshgupta410g@gmail.com

### **Abstract**

The emergence of the Internet of Things (IoT) and the widespread adoption of pervasive computing are poised to transform how we interact with our environment. This technological paradigm enables physical objects to not only collect and process data but also to communicate and exchange information over the Internet. This blending of the physical and cyber worlds is creating unprecedented opportunities, promising to revolutionize critical industries such as healthcare, transportation, infrastructure, and manufacturing. A key enabler for this revolution is the development of robust security protocols that offer minimal overhead and a small memory footprint, making them highly suitable for the resource-constrained devices that are central to IoT ecosystems.

Significant advancements in the miniaturization of sensors and micromachinery systems have opened a new frontier for researchers, allowing for the development of incredibly small microsystems for a wide range of applications. However, this progress is now confronting significant physical and power limitations. The drive toward further miniaturization to create smaller, more intelligent devices with enhanced functionality—especially for multi-task continuous computing—is being hindered by the challenge of providing adequate power.

Currently, these devices rely heavily on large, bulky batteries as their primary power source. The fundamental issue is that batteries have a fixed and limited energy capacity, which poses a critical challenge for designing and deploying next-generation, highly miniaturized devices. Overcoming this power constraint is a formidable, and in some cases, insurmountable obstacle to achieving the full potential of these advanced technologies. This pressing need for alternative power solutions is a major focus of ongoing research and development within the field.

### Introduction

Recent and profound advances across several key technological domains—specifically, sensor technologies, wireless communication systems, and embedded processors—have fundamentally enabled the conceptualization and design of a new generation of devices. These devices are characterized by their low cost, compact size, and minimal power consumption, all while possessing the essential capability to be networked or connected directly to the Internet. These combined features constitute the foundational components of the burgeoning technological paradigm known as the Internet of Things (IoT).

The scope of IoT is not only vast but is continually expanding, covering an ever-increasing range of critical applications. These deployments span diverse sectors, including high-precision health-care monitoring, large-scale smart city infrastructure, context-aware smart home environments, efficiency-optimized smart building management, and the automated processes defining the modern smart industry. This pervasive integration highlights the transformative potential of IoT to reshape both urban and industrial environments.

IoT devices are central to the overall functionality and development of this ecosystem. They are typically small, highly integrated packages, designed for immediate programming and deployment. Functionally, they combine essential components such as microcontrollers and microprocessors with necessary hardware, including various forms of memory, multiple I/O interfaces, supporting peripherals, and integrated wireless connectivity chips. The hardware landscape is diverse, encompassing both open-source hardware platforms, which encourage collaborative development, and proprietary solutions. The existence of well-established and adopted IoT standards has provided significant incentive for manufacturers to create these open hardware platforms, fostering greater innovation and interoperability within the market.

The Internet of Things, by definition, incorporates devices originating from a highly diverse and heterogeneous background. These devices demonstrate considerable variation across critical performance metrics, including physical size, available data storage, overall energy consumption, computational capacity, and required data rate. Crucially, seamless and interoperable communication across this varied network is facilitated by the sensors and actuators embedded within each unit. These miniature sensors are critical, as they assign a unique digital identifier to each participating physical device, thus integrating the physical systems into the digital network and significantly broadening the scope and scalability of today's Internet infrastructure.

The defining characteristic that fundamentally distinguishes embedded IoT devices from conventional embedded systems is their intrinsic connectivity, whether established via wired or wireless links. In its broader vision, the IoT is defined as a global, overarching infrastructure composed of heterogeneous, networked embedded objects and devices. This communication ability, especially Internet connectivity, empowers these smart objects (often referred to as machines) to communicate and interact in two primary modes: (i) autonomously with other machines and devices, or (ii) directly with human operators. Examples of these interconnected devices include highly sensitive environmental sensors, asset-tracking RFID tags, adaptive smart thermostats, and sophisticated smartphones and wearable gadgets. These devices are empowered to sense the environment, process the acquired data, and ultimately control or influence physical world events. Eventually, the expansion of the IoT is projected to lead to the Internet of Everything (IoE), a state where the virtual world of information is seamlessly and completely integrated with the physical world of objects.

## Low-Power Integrated Circuit Design Techniques for Digital, Analog, and Mixed-Signal IoT Hardware

1. The Core Imperative of Energy Efficiency in IoT Hardware

The maximization of the operational lifetime remains the most critical design constraint for the vast majority of Internet of Things (IoT) devices. Consequently, the most direct and effective strategy to enhance the battery life of an IoT device is through the profound reduction of power consumed by its constituent hardware components. This necessity extends even to devices, such as the Driblet and SPAN platforms, that utilize energy harvesting

techniques; for these systems, the use of ultra-low-power hardware is absolutely imperative to achieve the goal of near-perpetual operation. It is also valuable to recognize the architectural similarity between many modern IoT devices and established wireless sensor node platforms, which validates that the low-power design techniques refined for the latter are directly and equally applicable to the design of advanced IoT devices.

### 2. Power Dissipation Mechanisms in Digital Integrated Circuits

To effectively minimize the overall power consumption of the digital circuits within an IoT system, it is essential to first characterize the three distinct physical sources of power dissipation in CMOS logic. Understanding the contribution of each component is vital for implementing targeted minimization techniques. The total digital power dissipation, P, can be comprehensively expressed by the following equation:

$$P_{\text{Digital}} = \underbrace{V_{DD}I_{Leak}}_{\text{Stand-by power}} + \underbrace{C_{sc}V_{DD}^2f_{clk}}_{\text{Short-circuit power}} + \underbrace{\frac{1}{2}C_LV_{DD}^2f_{clk}E_{SW}}_{\text{Dynamic power}}, \tag{1}$$

In this expression,  $V_{DD}$  represents the supply voltage;  $C_L$  is the physical capacitive load being driven; and  $f_{clk}$  is the clock frequency of the system. The power components are defined by the following terms:

- Stand-by Current ( $V_{DD}I_{Leak}$ ): This is the DC current flowing continuously between the supply rails, even when the circuit is idle. It is fundamentally attributed to leakage current ( $I_{Leak}$ ) flowing through transistors when they are theoretically switched off.

- Short-Circuit Current ( $C_{SC}V^2_{DD}f_{clk}$ ): This dissipation occurs as a DC current between the supply rails during the finite transition period of a logic state. It arises when both the pull-up network (PMOS) and the pull-down network (NMOS) are simultaneously conducting, forming a momentary direct path between  $V_{DD}$  and ground. This effect is quantified by the equivalent short-circuit capacitance ( $C_{SC}$ ).

- Dynamic Current (1/2  $C_LV^2_{DD}f_{clk}E_{SW}$ ): This represents the dominant form of power consumption in active operation, resulting from the repeated charging and discharging of the capacitive loads ( $C_L$ ) during logic changes. This term is scaled by the switching activity ( $E_{SW}$ ), which is the average number of transitions per clock cycle.

# 3. The Criticality of Microcontroller State Management

Microcontrollers (MCUs) constitute the essential processing core of virtually every embedded system that must interface with and interact with the physical world, including all IoT devices. Many of these deployed systems are mandated to operate unattended for multiple years without the feasibility of battery replacement or external charging. Achieving this demanding operational lifetime necessitates extreme levels of energy efficiency across all modes of operation.

A crucial observation is that the typical IoT system spends greater than 90% of its total operational time in the sleep or idle mode. Consequently, the cumulative energy expenditure in this sleep state often forms the primary

SJIF Rating: 8.586 ISSN: 2582-3930

bottleneck determining the overall battery lifetime. This makes the selection of an MCU with exceptionally low power consumption in its idle state just as critical as its power efficiency during periods of active computation.

| Processors and MCUs (Freq = 8 MHz) |                        |                                      |       | Wireless Standards                  |            |                       |        | Sensors       |          |                        |                      |

|------------------------------------|------------------------|--------------------------------------|-------|-------------------------------------|------------|-----------------------|--------|---------------|----------|------------------------|----------------------|

| Product                            | Architecture<br>Family | Current<br>Active Sleep<br>(mA) (µA) |       | Standard<br>(Product)               | Tx<br>(mA) | Current<br>Rx<br>(mA) | Sleep  | Sensor        | Product  | Curr<br>Active<br>(µA) | ent<br>Sleep<br>(μA) |

| MSP430F5438A                       | MSP430                 | 1.84                                 | 0.1   | 200000                              | Cinci      | (mer)                 | /here) | Temperature   | TMP102   | 85                     | 0.5                  |

| STM32L051x6                        | ARM CM0+               | 1.55                                 | 0.29  | WiFi<br>(TI CC3200)                 | 229        | 59                    | 4      | Humidity      | SHT21    | 300                    | 0.15                 |

| STM32L100C6                        | ARM CM3                | 2.16                                 | 0.3   | IEEE 802.15.4<br>(Atmel AT86RF231)  | 14         | 12.3                  | 0.02   | Accelerometer | ADXL362  | 13                     | 0.01                 |

| SAM4S                              | ARM CM4                | 4.5                                  | 1.8   |                                     |            |                       |        | Light         | ISL29033 | 65                     | 0.01                 |

| PIC24FJ128GC010                    | PIC                    | 1.5                                  | 0.075 | Bluetooth Smart<br>(Nordic nRF8001) | 12.7       | 14.6                  | 0.5    | Proximity     | AD7150   | 100                    | 1                    |

Table 1: Power consumption of a few representative hardware components used in IoT devices (sourced from datasheets).

To address this challenge, most modern MCUs are equipped with a variety of low-power (or sleep) modes. For instance, certain hardware series, such such as the STM32L1 family of MCUs (based on the ARM Cortex M3 core), support up to seven distinct operational sleep modes. These modes are generally categorized into two primary types:

- Shallow Sleep Mode: In this state, the MCU core is halted, most peripherals are disabled, and main clock sources are turned off. Crucially, the MCU remains partially powered up, which ensures that all essential state information—including the values in the MCU registers and the data stored in the onchip SRAM—is preserved during the sleep cycle. While the wake-up time from shallow sleep is extremely fast, it does not represent the absolute lowest power consumption achievable.

- Deep Sleep Mode: This is the most aggressive low-power state, involving the power-down of the entire MCU, including the internal on-chip SRAM block. While this results in the lowest possible power consumption during the sleep period, the primary trade-off is the loss of SRAM state, requiring the system to perform a more comprehensive initialization upon wake-up.

- 4. Unique Challenges in Low-Voltage Analog Circuit Design

The implementation of low-voltage operation in the analog circuitry of an IoT device presents challenges that are significantly different from those encountered in the digital domain. For instance, when the supply voltage (V<sub>DD</sub>) is reduced toward the near-threshold voltage of the MOSFETs, the available overdrive voltage (OV), or voltage headroom, becomes severely limited. This limitation can introduce a significant and undesirable temperature shift in the cutoff frequency of the MOS transistor, which consequently hinders the predictable performance of the entire analog circuit block.

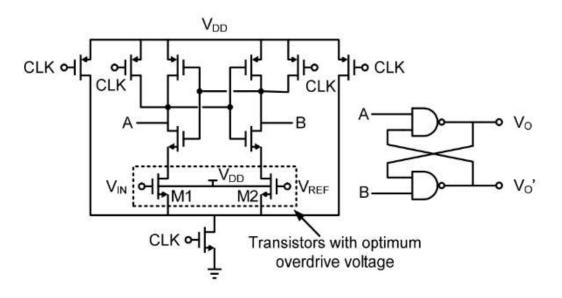

To counteract this critical temperature drift issue, specialized design techniques are employed. For example, research by Lin and Yuan focused on utilizing an optimum overdrive voltage to mitigate temperature sensitivity. By leveraging the mutual temperature compensation of carrier mobility and threshold voltage, it becomes possible to identify an optimal bias point that renders the transistor's cutoff frequency largely insensitive to temperature variations, thereby ensuring robust analog performance under varying environmental conditions. Furthermore, the use of emerging devices such as Tunnel Field-Effect Transistors (TFETs) has demonstrated potential to significantly enhance analog circuit performance under extreme low-power constraints.

Volume: 09 Issue: 11 | Nov - 2025 SJIF Rating: 8.586 **ISSN: 2582-3930**

Figure . Schematic of the comparator using the optimum overdrive voltage technique

## 5. Analog-to-Digital Conversion: The Power-Hungry Interface

IoT devices that are intended to be deployed and accessed from any location and at any time require ultra-low energy efficiency for all primary functions: sensing, communication, and computing. The Analog-to-Digital Converter (ADC) is one of the most essential and ubiquitous building blocks for the sensor interface, tasked with reliably digitizing the analog output of the sensor for subsequent digital signal processing. In many wireless IoT applications, the power supply is derived from energy harvesting devices such as solar cells, which can typically generate only an extremely low output voltage, often less than 0.5 V. This makes ultra-low-voltage and ultra-low-power operation absolutely critical.

These applications often require ADCs with moderate resolution and speed (typically 1 kHz to 1000 kHz), while the incoming signal level from the sensor is also generally small. Given these constraints, ADCs are frequently identified as the most critical and power-hungry blocks within the sensor node, necessitating focused design optimization efforts.

### SAR ADC Clocking Scheme Detail

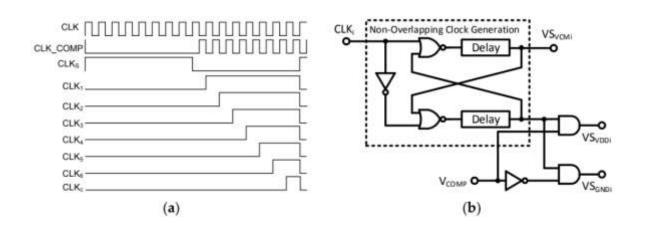

The Successive Approximation Register (SAR) ADC is a popular choice for low-power IoT applications. The complex clock scheme required for its operation is meticulously designed to manage the sampling and decision phases. This scheme utilizes several key clock signals:

- CLK: The external, main clock signal that dictates the overall timing.

- CLK COMP: The clock signal specifically timed to trigger the comparator for a decision.

- CLKS: The sampling clock, which controls the duration of the sampling phase.

- CLK<sub>i</sub>: A sequence of clocks that control the feedback switch of the capacitor C<sub>i</sub> within the DAC array.

For instance, if the sampling period is eight clock cycles, this provides sufficient time for the sampling circuit to settle accurately. When the sampling clock (CLKS) is high, the comparator is temporarily disabled, and the

capacitor's bottom plate is connected to the common mode voltage ( $V_{CM}$ ). When CLKS transitions to low, the top plate of the capacitor array is isolated, and the comparator initiates the comparison process.

The specific decision-making is controlled by  $CLK_i$ , which becomes high after the  $i^{th}$  decision is finalized. This clock then switches the bottom plate of  $C_i$  to either  $V_{DD}$  or GND based on the comparator's output. A vital component is the non-overlapping clock generation module , which processes  $CLK_i$  to guarantee that the bottom plate of capacitor  $C_i$  will not be connected to both  $V_{CM}$  and either  $V_{DD}$  or GND simultaneously, thereby preventing destructive shorts or corrupted data. The signals VSVCMi, VSVDD, and VSGND serve as the control signals for the switches that govern the connection of the bottom plate of capacitor  $C_i$  to  $V_{CM}$ ,  $V_{DD}$ , and GND, respectively. The output voltage of the comparator, VCOMP, directly determines whether the bottom plate of  $C_i$  is ultimately switched to  $V_{DD}$  or GND for the current bit decision.

Figure . (a) Clock timing; (b) Clock generating logic

# A Holistic Approach to IoT Energy Efficiency

The maximization of the operational lifetime is the most critical design constraint for the vast majority of Internet of Things (IoT) devices, many of which must operate unattended for multiple years without battery replacement. Therefore, achieving extreme energy efficiency is the core imperative for all hardware components, from the processing core to the sensor interface. This necessity extends even to systems utilizing energy harvesting, where ultra-low-power hardware is absolutely imperative to achieve the goal of near-perpetual operation.

1. Energy Efficiency at the System Level: Microcontroller State Management

The key to system-level energy efficiency lies in effectively managing the microcontroller's (MCU) operational states.

• Sleep State Dominance: A typical IoT system spends greater than 90% of its total operational time in the sleep or idle mode.

- Primary Bottleneck: Consequently, the cumulative energy expenditure in this sleep state often forms the primary bottleneck determining the overall battery lifetime. This makes selecting an MCU with exceptionally low idle power consumption as critical as its active efficiency.

- Low-Power Modes: Modern MCUs offer distinct low-power modes with trade-offs:

- Shallow Sleep Mode: The MCU core and main clocks are halted, but essential state information (registers, SRAM data) is preserved because the MCU remains partially powered. This allows for extremely fast wake-up time.

- O Deep Sleep Mode: This is the most aggressive state, resulting in the lowest possible power consumption by powering down the entire MCU, including the on-chip SRAM. The tradeoff is the loss of SRAM state, requiring a more comprehensive re-initialization upon wake-up.

- 2. Energy Efficiency in Analog and Mixed-Signal Blocks

The Analog-to-Digital Converter (ADC) is often identified as one of the most critical and power-hungry blocks within a sensor node, especially for ultra-low-voltage systems powered by energy harvesting.

- Low-Voltage Challenges: Reducing the supply voltage  $(V_{DD})$  toward the near-threshold voltage severely limits the available overdrive voltage (OV) or voltage headroom in analog circuits.

- Temperature Drift: This limitation can introduce a significant and undesirable temperature shift in the cutoff frequency of the MOS transistor, which can hinder the predictable performance of the entire analog block.

- Compensation Technique: A crucial strategy to counteract this is the use of an optimum overdrive voltage to leverage the mutual temperature compensation of carrier mobility and threshold voltage, which renders the transistor's cutoff frequency largely insensitive to temperature variations, ensuring robust analog performance.

### **CONCLUSION**

The Internet of Things (IoT) stands as a transformative technological paradigm, poised to revolutionize critical sectors by blending the physical and cyber worlds. However, this paper has argued that the full realization of its potential—from smart healthcare and transportation to pervasive smart city infrastructure—is fundamentally constrained by the critical challenge of power. The reliance on large, capacity-limited batteries presents a formidable obstacle, making the maximization of operational lifetime the single most critical design constraint for the vast majority of IoT devices.

This work has provided a comprehensive survey of the essential low-power Integrated Circuit (IC) design techniques required to address this challenge. Our review spanned the full stack of IoT hardware, demonstrating that a holistic design approach is not merely beneficial but imperative.

We have shown that effective power minimization in digital circuits requires a deep understanding of all three dissipation sources: stand-by leakage, short-circuit current, and dynamic switching power. For the system-level

microcontroller (MCU), we identified that the sleep state is the primary bottleneck for battery life, as devices spend over 90% of their time in this mode. Consequently, the intelligent management of low-power modes, balancing the trade-offs between "Shallow Sleep" (state retention) and "Deep Sleep" (lowest power), is a paramount design consideration.

In the analog domain, this paper highlighted the unique challenges of low-voltage operation, where limited voltage headroom can introduce significant temperature sensitivity. The solution, as discussed, lies in advanced techniques such as using an "optimum overdrive voltage" to achieve temperature-insensitive performance through mutual compensation.

Finally, we identified the Analog-to-Digital Converter (ADC) as one of the most critical and power-hungry blocks in a sensor node, especially for systems relying on ultra-low-voltage energy harvesting. The detailed analysis of a Successive Approximation Register (SAR) ADC demonstrated that sophisticated clocking schemes, including non-overlapping clock generation, are essential for achieving high efficiency at this vital interface.

As underscored in our review of related work, this paper fills a unique gap by consolidating these multi-domain techniques, which are often discussed in isolation. The path forward to a truly pervasive "Internet of Everything" (IoE) depends on the successful integration of these strategies.

### **FUTURE PRESPECT**

Future research must continue to push the boundaries of energy efficiency to achieve the goal of near-perpetual operation. We identify two critical areas for further investigation:

- 1. Exploitation of Emerging Devices: This paper briefly noted the potential of devices like Tunnel Field-Effect Transistors (TFETs). Dedicated research into the design and integration of TFETs and other novel components into analog and digital IoT circuits could yield significant reductions in power consumption beyond what is possible with conventional CMOS.

- 2. Robust Ultra-Low-Voltage Design: As energy-harvesting sources often provide less than 0.5 V, the design of robust, high-performance analog and mixed-signal circuits (particularly ADCs) that can operate reliably in this regime remains a significant challenge(Martins et al, 2018). Future work should focus on new architectures and compensation techniques to overcome the limitations of near-threshold operation.

By building upon the holistic design principles outlined in this paper and pursuing these future directions, the research community can successfully overcome the power bottleneck and unlock the full potential of the Internet of Things.

### **REFERENCES**

Martins, G. C., Urso, A., Mansano, A., Liu, Y., & Serdijn, W. A. (2018). Energy-Efficient Low-Power Circuit Techniques for Wireless Energy and Data Transfer in IoT Sensor Nodes.

Henkel, J., Pagani, S., Amrouch, H., Bauer, L., & Samie, F. (2017). Ultra-Low Power and Dependability for IoT Devices. 2017 Design, Automation & Test in Europe Conference & Exhibition (DATE), 954–959.

Ojo, M. O., Giordano, S., Procissi, G., & Seitanidis, I. N. (2018). A Review of Low-End, Middle-End, and High-End IoT Devices. IEEE Access, 6, 70528–70554.

Yuan, J.-S., Lin, J., Alasad, Q., & Taheri, S. (2017). Ultra-Low-Power Design and Hardware Security Using Emerging Technologies for Internet of Things. Electronics, 6(3), 67.

Jayakumar, H., Lee, K., Lee, W. S., Raha, A., Kim, Y., & Raghunathan, V. (2014). Powering the Internet of Things. Proceedings of the 2014 International Symposium on Low Power Electronics and Design, 375–380.

Lundager, K., Zeinali, B., Tohidi, M., Madsen, J. K., & Moradi, F. (2016). Low Power Design for Future Wearable and Implantable Devices. Journal of Low Power Electronics and Applications, 6(4), 20.