# **N-Bit ALU Design Using Vedic Mathematics**

M Ramakrishna<sup>1</sup>, K Harini<sup>2</sup>, N AkhilSai<sup>3</sup>, G Ramu<sup>4</sup>, T Rakesh<sup>5</sup>

<sup>1</sup>Electronics and communication ,jyothishmathi institute of technology and science <sup>2</sup>Electronics and communication ,jyothishmathi institute of technology and science <sup>3</sup>Electronics and communication ,jyothishmathi institute of technology and science <sup>4</sup>Electronics and communication ,jyothishmathi institute of technology and science <sup>5</sup>Electronics and communication ,jyothishmathi institute of technology and science <sup>\*\*\*</sup>

**Abstract** - The Arithmetic and Logic Unit (ALU) is a central component in modern computing systems, responsible for performing core arithmetic and logical operations. This paper proposes an N-bit ALU designed using Vedic mathematical principles to achieve improved speed and reduced power consumption. Leveraging the Urdhva Tiryakbhyam principle from Vedic mathematics, the ALU integrates an efficient multiplier along with high-performance arithmetic and logic units. The architecture, developed using Verilog HDL and synthesized through Xilinx Vivado, exhibits lower delay and efficient hardware usage, making it well-suited for applications in embedded systems and signal processing.

*Key Words*: Vedic Mathematics, N-Bit ALU, Urdhva Tiryakbhyam Algorithm, Verilog HDL Implementation, High-Speed Multiplication, FPGA Synthesis.

#### **1.INTRODUCTION**

The advancement of semiconductor technology has enabled the integration of a large number of components on compact chips, facilitating the growth of power-efficient and performance-optimized embedded systems. Among these, the Arithmetic Logic Unit (ALU) plays a pivotal role in microprocessors, being responsible for executing both arithmetic and logical instructions. Given its continuous operation and critical placement within the CPU, optimizing the ALU for power and speed is essential.

This paper presents an N-bit ALU that leverages the computational efficiency of Vedic mathematics, particularly the Urdhva Tiryakbhyam Sutra, to implement faster arithmetic operations. The design methodology focuses on achieving minimal delay and efficient resource utilization, contributing to energy-efficient hardware design for real-time and low-power applications.

#### 2. LITERATURE SURVEY

Previous studies have explored the benefits of Vedic multipliers in reducing computation delay and improving hardware efficiency. Vijay Kumar Reddy's work on binary Vedic multipliers demonstrated performance gains in 4-bit to 16-bit configurations. Other contributions include approximate multiplier designs by Momeni et al., configurable recovery techniques by Liu et al., and speculative addition strategies by Cilardo et al. These approaches share the objective of balancing speed, accuracy, and power in arithmetic operations, particularly in error-tolerant and multimedia applications.

#### **3. METHODOLOGY**

The designed ALU comprises multiple modular units, each tailored to deliver high efficiency and minimal hardware footprint. Verilog HDL was used for design, while simulation and synthesis were performed using ModelSim and Xilinx Vivado, respectively.The primary functional components are outlined as follows:

#### 3.1 Adder/Subtractor Unit

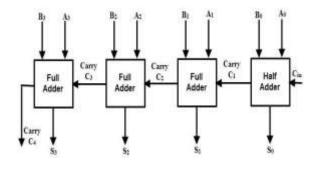

The adder module utilizes a Ripple Carry Adder (RCA) configuration, in which individual 1-bit full adders are linked in sequence to handle operations on multi-bit inputs. Each stage produces a sum and propagates the carry to the next stage, forming a ripple-like behaviour from the least to the most significant bit. This method offers a simple and easily scalable structure, though it may introduce carry propagation delay. The subtraction operation is implemented by leveraging the existing adder unit, using two's complement transformation on the subtrahend.

Fig-1: Ripple Carry Adder

#### **3.2 Vedic Multiplier Unit**

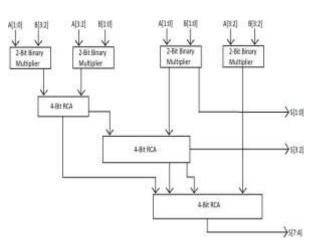

The multiplication block is based on the Urdhva Tiryakbhyam Sutra, a parallel processing technique from Vedic mathematics. This algorithm allows simultaneous generation of partial products and reduces the depth of addition stages. Summation is handled by ripple carry adders. This design reduces hardware overhead and improves processing speed, making it well-suited for space-efficient ALU implementations.

International Journal of Scientific Research in Engineering and Management (IJSREM)

Volume: 09 Issue: 05 | May - 2025

SJIF Rating: 8.586

ISSN: 2582-3930

Fig-2: 4-Bit Vedic Multiplier

## 3.3 Logical Unit

This component handles bit-level logical functions, including operations like AND, OR, XOR, NAND, NOR, NOT, and XNOR.. A multiplexer-based control logic is used to dynamically select the required operation based on control signals.

## **3.4** Comparator

The comparator evaluates two binary numbers and produces outputs for A > B, A = B, and A < B. It analyzes the bits starting from the most significant to the least significant position and uses priority logic to determine the output. This component plays a crucial role in managing control flow and enabling branching within processors.

Fig-3: Block Diagram of Comparator

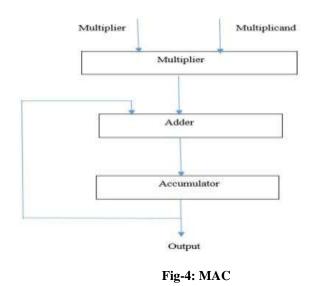

## 3.5 MAC Unit

The Multiply-Accumulate (MAC) unit plays a crucial role in digital signal processing and multimedia applications. It operates on 4-bit input values from memory, utilizing a Vedic multiplication method to generate an 8-bit product.

The result is then added using an adder and stored in a Parallel-In Parallel-Out (PIPO) register. This arrangement supports fast, concurrent input-output handling, making it suitable for real-time digital signal operations.

#### 4. Results

The design was synthesized using Xilinx Vivado and validated through simulation in ModelSim. The findings demonstrate notable enhancements in both delay reduction and power efficiency compared to conventional ALU designs.

| Table 1: Resource Utilization and Performance |  |  |

|-----------------------------------------------|--|--|

| Comparison                                    |  |  |

| Parameters | Basic<br>Approach | Proposed<br>Approach |

|------------|-------------------|----------------------|

| Power      | 4.342W (97%)      | 3.934W (93%)         |

| Delay      | 32.5ns            | 14.2ns               |

| Speed      | Less              | Fast                 |

Fig-7: Simulation Waveforms.

T

### **5. CONCLUSION**

Computational methods based on Vedic Mathematics have shown greater efficiency than traditional approaches, especially in the field of signal processing. The designed ALU employs the Urdhva-Tiryakbhyam Sutra for multiplication, complemented by optimized circuits for addition and logic functions. This architecture enhances performance and is wellsuited for modern signal processing tasks. In the future, such designs can be used to upgrade outdated integrated circuits, minimizing hardware modifications, improving productivity, and ensuring adherence to performance constraints.

### **REFERENCES:**

[1] S. Akhter, "VHDL implementation of fast NxN multiplier based on Vedic mathematics,"in Proc. 18th European Conference on Circuit Theory and Design, 2007, pp. 472-475

[2] S. Nagaraj, Dr.G.M. Sreerama Reddy and Dr.S. Aruna Mastani; A Comparative Study on Different Multipliers-Survey Journal of Advanced Research in Dynamical and Control Systems14739-7522018Institute of Advanced Scientific Research.

[3] M.Pushpa, S. Nagaraj, Design and Analysis of 8-bit Array, Carry Save Array, Braun, Wallace Tree and Vedic Multipliers, IEEE Sponsored International ConferenceOn New Trends In Engineering & Technology (ICNTET 2018).

[4] Nagaraj, S; Thyagarajan, K; Srihari, D; Gopi, K; Design and Analysis of Wallace Tree Multiplier for CMOS and CPL Logic2018 International Conference on Computation of Power, Energy, Information and Com- munication (ICCPEIC)006-0102018IEEE

[5] Josmin Thomas ; R. Pushpangadan ; S Jinesh Comparative study of performance Vedic multiplier on the Basis of Adders used 2015 IEEE International WIE Conference on Electrical and Computer Engineering (WIECON-ECE)

[6] S. Nagaraj, Dr.G.M. Sreerama Reddy and Dr.S. Aruna Mastani; A Survey on Adiabatic Logic International Conference on Communications, Signal Processing and VLSI(IC2SV2019), Springer Conference, National Institute of Technology, Warangal.

T