Volume: 09 Issue: 05 | May - 2025 SJIF Rating: 8.586 ISSN: 2582-3930

# Optimization of Efficiency and Parameters of Dc-Dc Converter Using Enhanced Jaya Algorithm

# H. AAISHA SIDHIKA<sup>1</sup>

<sup>2</sup>PG Scholar, Dept. Of EEE, M.I.E.T Engineering College, Trichy, India

**Abstract** - This project presents a comparative efficiency optimization of DC-DC power converters using the Jaya and Enhanced Jaya algorithms. DC-DC converters are essential in power electronics, requiring precise tuning of parameters such as switching frequency, duty cycle, inductance, and capacitance to improve efficiency and reduce losses. Traditional optimization methods often face limitations like slow convergence and entrapment in local optima.

The Enhanced Jaya algorithm addresses these issues through a dynamic, adaptive search mechanism that improves convergence speed and global optimization performance. It is applied to various DC-DC converter topologies, targeting key performance metrics including efficiency, output ripple, and transient response.

Simulation results demonstrate that the Enhanced Jaya algorithm consistently outperforms conventional optimization techniques, achieving better parameter tuning and enhanced overall converter performance. This optimization approach shows strong potential for real-world applications in renewable energy, electric vehicles, and industrial power systems.

**Key Words:** DC-DC Converters, Enhanced Jaya Algorithm, Efficiency Optimization, Power Electronics, Techniques, Transient Response, Renewable Energy Systems

### 1. INTRODUCTION

The growing demand for high-efficiency power conversion systems has driven significant advancements in DC-DC converter technology. These converters are vital in applications such as renewable energy systems, electric vehicles, and portable electronics. Their performance is influenced by parameters like switching frequency, duty cycle, and component values, all of which must be optimized to enhance efficiency and minimize power losses.

Traditional optimization techniques often struggle to meet the competing demands of efficiency and performance, particularly in complex, nonlinear systems. In response, metaheuristic algorithms have emerged as effective tools for addressing such challenges. Among them, the Jaya Algorithm has gained attention due to its simplicity, ease of implementation, and independence from problem-specific parameters or gradient information. However, its basic form may exhibit slow convergence and suboptimal performance in complex design spaces.

This project introduces the Enhanced Jaya Algorithm (EJA) to optimize key performance metrics—efficiency, power loss, and transient response—across various DC-DC converter

topologies. EJA incorporates adaptive improvements to boost convergence speed and solution accuracy. Through simulation and testing, the study aims to demonstrate EJA's effectiveness in delivering robust, energy-efficient converter designs suitable for real-world applications in advanced power electronics.

#### 2. GENERAL DISCRIPTION

The **Enhanced Jaya Algorithm** (**EJA**) is an advanced metaheuristic optimization technique designed to improve the performance of **DC-DC converters**. It optimizes key parameters like duty cycle and switching frequency to reduce power loss, minimize voltage ripple, and enhance transient response—all without requiring gradient information. EJA improves upon the basic Jaya algorithm by incorporating better exploration and exploitation strategies, ensuring faster convergence and higher solution accuracy.

The algorithm works by:

- 1. **Initializing** a population of potential solutions,

- 2. **Evaluating** their performance based on defined objectives (e.g., efficiency),

- 3. **Iteratively updating** solutions using improved rules, and

- 4. **Converging** when optimal or near-optimal performance is achieved.

EJA effectively navigates complex design spaces, making it suitable for real-world converter applications that demand high efficiency, stability, and robustness.

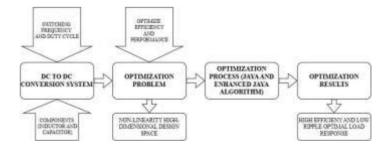

**Figure -1:** Systematic diagram of DC-DC Converter optimization

© 2025, IJSREM | www.ijsrem.com | Page 1

Volume: 09 Issue: 05 | May - 2025

#### SJIF Rating: 8.586

#### ISSN: 2582-3930

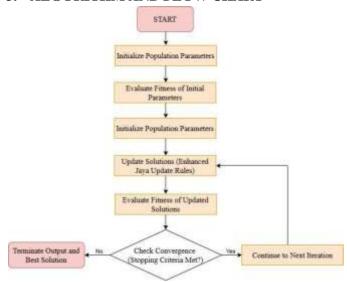

#### 3. ALGORITHM AND FLOW CHART

$Xi(t+1)=Xi(t)+\alpha.r1.(Xbest(t)-Xi(t))-\beta.r2.(Xworst(t)-Xi(t))$

#### ) Where:

- $\alpha$  and  $\beta$  are adaptive coefficients that influence the update magnitude and allow for more exploration or exploitation based on the current iteration.

- r1, r2: Random numbers in the range [0,1]

- Xi(t): Current solution of i-th individual at iteration t

- Xbest(t): Global best solution at iteration t

- Xworst(t): Worst solution at iteration t

#### **Initialize Population:**

Randomly initialize a population of solutions (parameter values for the DC-DC converter).

#### **Evaluate Fitness:**

For each solution in the population, evaluate the fitness using the objective function (e.g., converter efficiency, voltage regulation, or ripple minimization.

#### **Find Best and Worst Solutions:**

Find the solution with the best fitness value: Xbest Find the solution with the worst fitness value: Xworst **Update**

# **Solutions:**

For each individual Xi in the population, update its position using the Enhanced Jaya update rule:

$$Xi(t+1)=Xi(t)+\alpha.r1.(Xbest(t)-Xi(t))-\beta.r2.(Xworst(t)-Xi(t))$$

# **Termination Condition:**

Repeat steps 2-4 until a stopping criterion is met (e.g.,

maximum number of iterations, acceptable performance level, or convergence).

# **Output:**

The algorithm returns the best solution found.

# 4. OPTIMIZING BUCK-BOOST CONVERTER PARAMETERS USING EJA

# I. Design Specifications – Buck Mode (For Example):

- Input Voltage (Vin): 18 V

- Output Voltage (Vout): 12V

- Switching Frequency (fsw): 40 kHz

- Resistance(R):10ohm

- Efficiency (η): 90% (target efficiency)

- Inductor ripple current: 1% of output current (for design purpose)

Manual Calculation Result:

1. Duty Cycle (D)

$$D = \frac{Vo}{Vo + Vin}$$

$D = 12/(12+18)$

$D = 0.4$

2. Input Current (*Iin*)

$$Iin = \frac{Po}{Vs}$$

$$Iin = 14.4/18$$

$Iin = 0.8 A$

3. Output Current (Io)

$$Io = \frac{Vo}{R}$$

$$Io = 12/10$$

$$Io = 1.2 \text{ A}$$

4. Inductor (*L*)

$$Lmin = \frac{R(1-D)^2}{2fs}$$

$$Lmin = 0.6/80000$$

$$Lmin = 0.45\mu H$$

5. Inductor Ripple Current

$$\Delta IIL = Vs. D/L.fs$$

$\Delta IIL = (18 * 0.4)/(0.0001*40000)$

$\Delta IIL = 1.8A$

6. Capacitor (C)

$$C = \frac{C}{f} \cdot \Delta Vo$$

$C = 12 * 0.4/40000 * 0.48$

$C = 20\mu F$

7. Peak Inductor Current (*Ipeak*)

$$I_l \ peak = I_{avg} + (\frac{\Delta I_L}{2})$$

$I_l \ peak = 0.8 + (\frac{1.8}{2})$

$I_l \ peak = 1.7A$

8. Efficiency

© 2025, IJSREM | www.ijsrem.com | Page 2

Volume: 09 Issue: 05 | May - 2025

SJIF Rating: 8.586

$\eta_{Ideal} = \frac{P_{in}}{P_{ou}} = (V_{in}.I_{in})/(V_o.I_o)$  1494.1%

Enhanced Jaya Algorithm Result:

- 1. Inductor (L) =  $165 \mu H$

- Capacitor (C) =  $40 \mu F$

- Efficiency = 16%

# II. Design Specifications - Boost Mode (For Example):

- Input Voltage (Vin): 18 V

- Output Voltage (Vout): 27V

- Switching Frequency (fsw): 40 kHz

- Resistance(R):10ohm

- Efficiency (η): 90% (target efficiency)

- Inductor ripple current: 1% of output current (for design purpose)

Manual Calculation Result:

1. Duty Cycle (D)

$$D = \frac{Vo}{Vo + Vin}$$

$$D = \frac{27}{(27+18)}$$

$$D = 0.6$$

Input Current (Iin)

$$Iin = 72.9/18$$

$$Iin = 4.05 \text{ A}$$

3. Output Current

(Io)

$$Io = \frac{Vo}{R}$$

$$Io = 27/10$$

$$Io = 2.7 \text{ A}$$

4. Inductor (L)

$$Lmin = \frac{R(1-D)^2}{2fs}$$

$$Lmin = 1.6/80000$$

$$Lmin = 220 \mu H$$

5. Capacitor (C)

Capacitor (c)

$$C = \frac{D}{f} \cdot \Delta Vo$$

$$I. \qquad s$$

$$C = 2.7 * 0.6/40000 *1.62$$

$$C = 47\mu F$$

6. Peak Inductor Current (*Ipeak*)

$$I_l peak = I_{avg} + (\frac{\Delta I_L}{2})$$

$$I_l peak = 4.05 + (\frac{1.215}{2})$$

$I_l peak = 4.455A$

7. Efficiency

$$\begin{split} \mathcal{W} &= \frac{P_{in}}{-} = \quad \quad . \quad )/(V \cdot I) \\ &\stackrel{Ide}{al} \quad P_o \qquad \quad \begin{matrix} I \\ i & i & o & o \end{matrix} \\ & \begin{matrix} ut \\ 72 \\ 9 \end{matrix} \\ & \begin{matrix} \eta_{Ideal} \end{matrix} = \begin{matrix} \gamma_{4.8} \\ \eta_{Ideal} \end{matrix} = 97.4\%$$

Enhanced Jaya Algorithm Result:

- 4. Inductor (L) =  $220 \mu H$

- 5. Capacitor (C) =  $67 \mu F$

- 6. Efficiency = 98.79%

#### 5. CONCLUSIONS

The design of a DC-DC Buck Converter involves selecting the appropriate components based on input/output components specification, optimizing the converter for efficiency, and verifying the design using simulation. You can further optimize the parameters using optimization algorithms lie the Enhanced Jaya Algorithm to improve performance and ensure reliability under varying conditions.

# **REFERENCES**

- L.A. Bryan and E.A.Bryan, "Programmable Controllers: Theory And Implementation", Industrial Text, Chicago, IL,1998, pp20-40.

- 2. R.A. Cox, Technicians Guide To Programmable Logic Controllers.4th Ed., Delmar Thomson Learning, Inc. 2001.

- 3. A beginner's guide to PLC, delta automation ltd.

- Naveen Kumar P, Naveen Kumar K, Arvind M, Senthilraja S,"Smart Home using PLC", IJRASET, VOL 4, issue 8, Aug

© 2025, IJSREM | www.ijsrem.com Page 3