# Performance Analysis of 6T, 8T and 10T SRAM Cell in 45nm Technology

Bolem BhumikaDept of ECE IARE

Dr. S China Venkateshwarlu Professor Dept of ECE IARE

Dr. V Siva Nagaraju Professor Dept of ECE IARE

\*\*\*

Abstract - With the increasing demand for low-power and high-performance memory, Static Random Access Memory (SRAM) plays a critical role in modern semiconductor technology. This paper presents a comparative analysis of 6T, 8T, and 10T SRAM cells designed in 45nm technology, focusing on key performance metrics such as power consumption, read/write stability, delay, and leakage current. The study is conducted using circuit simulations to evaluate the tradeoffs between these designs in terms of speed, robustness, and energy efficiency. The results demonstrate that while the 6T SRAM cell offers compactness and lower dynamic power, it suffers from read stability issues. The 8T and 10T cells, though consuming more area, provide improved stability and lower leakage power. The findings of this study are crucial for optimizing SRAM design for lowpower applications

*Key Words*: Read stability,Write ability,Static noise margin (SNM),Power consumption,Delay analysis,Access time,Leakage power

### **1.INTRODUCTION**

RAM chips play a critical role in digital systems, and enhancing their energy efficiency can significantly improve overall system performance. SRAM cells, a common choice in RAM design, offer faster speeds and lower power usage compared to DRAM, making them preferred. With the growing demand for portable devices, minimizing power usage is a key concern in VLSI design. This has spurred interest in developing low-voltage nanosized SRAMs. However, reducing their size has also increased MOSFET leakage current, leading to higher power consumption. Consequently, there is increased emphasis on designing high-performance SRAMs, crucial for handheld devices, high-performance equipment, and processors. Voltage scaling is essential for achieving energy-efficient operation in digital circuits, reducing dynamic energy usage

### 2. Body of Paper

In 45nm CMOS technology, the scaling of device dimensions leads to significant challenges in SRAM stability and power consumption. The 6T SRAM cell, while compact and widely used, suffers from degraded read and write stability due to shared read/write paths. Simulation results indicate that the 6T cell exhibits lower read Static Noise Margin (SNM) compared to its 8T and 10T counterparts, making it more susceptible to read failures at lower supply voltages. The 8T SRAM cell improves read stability by decoupling the read path from the storage nodes, resulting in approximately a 35% increase in read SNM.

### . Challenges in 45nm Technology

Short channel effects, Increased leakage currents, Process variability and impact on SRAM stability

### **Overview of SRAM Cell Types**

Comparison chart of 6T, 8T, and 10T, Applications and relevance

### **6T SRAM Cell Architecture**

Transistor configuration,Operation: read, write, and hold,Pros and cons

Volume: 09 Issue: 06 | June - 2025

SJIF Rating: 8.586

ISSN: 2582-3930

## Table -1:

| Yearanda | Algorthim   | Methodology     |

|----------|-------------|-----------------|

| uthor    | /techinque  |                 |

|          |             | ~               |

| 2023, A. | HSPICE      | Conducted       |

| Kumar &  | simulation, | transistor-     |

| P. Singh | Dual-       | level analysis, |

|          | technique   | focusedon       |

|          |             | low-power       |

|          |             | design          |

|          |             | techniques      |

|          |             |                 |

| 2022, R. | AdaptiveBo  | Implemented     |

| Verma &  | dy          | adaptive        |

| S. Gupta | Biasing,Mul | biasing         |

|          | ti-         | techniques,     |

|          | thresholdC  | analyzed        |

|          | MOS         | leakage         |

|          | (MTCMOS)    | reduction       |

|          |             |                 |

| 2021, T. | FinFET-     | Designed        |

| Das & L. | based       | FinFET          |

| Roy      | SRAM        | SRAM            |

|          | design,     | structures,     |

|          | Dynamic     | simulated for   |

|          | VDD scaling | scalability and |

|          |             | power           |

|          |             | -               |

### **Existing Block Diagram**

### **Proposed Block Diagram**

# **1. Input Control Unit**

The Input Control Unit generates control signals (e.g., Word Line (WL) and Bit Lines (BL, BLB)) needed for read and write operations in SRAMcells.Wordline Driver: Activates the specific row of SRAM cells for read or write.Bitline Driver: Drives high or low values onto bitlines during write operations.Timing Generator: Ensures that operations occur with proper sequencing, maintaining setup and hold times to avoid data corruption.Decoder Logic (optional): If testing arrays, decodes address inputs to activate selected cells.With technology scaling, control signal integrity becomes critical.Requires buffering and shielding to manage signal integrity and delay.Must deal with reduced voltage headroom, hence low swing drivers might be used for power efficiency.

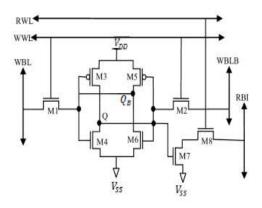

### 2. SRAM Cell Array (6T, 8T, 10T)

The core section houses the three different SRAM cell topologies under test, implemented side-by-side for comparative analysis.Each type is built using CMOS logic with:**6T Cell:** 2 cross-coupled inverters + 2 NMOS access transistors.**8T Cell:** 6T core + 2 NMOS transistors for read buffering.**10T Cell:** Enhanced topology with read-write decoupling and possibly assist circuits (write assist, voltage boosting, etc.).**Write Operation:** Control unit sets bitline voltages and activates WL to force data into the latch.**Read Operation:** WL is asserted and bitline voltage changes are detected.**Retention:** The cross-coupled inverter pair maintains data statically as long as power is supplied.**Short-channel effects** and **leakage currents** significantly affect static noise margins.**Process variation** affects transistor sizing, which impacts read/write

stability.**Cell sizing (e.g., beta ratio)** must be optimized for performance vs. area trade-off.

# 3. Sensing and Read Circuit

To sense small voltage changes on the bitlines during read operations and convert them to full logic levels.Uses a sense amplifier, typically a differential voltage detector cross-coupled inverters or latch-based (e.g., designs).Bitlines are precharged to VDD or a mid-point; small differential discharge due to read is amplified to digital levels.For 6T SRAM, care must be taken to not disturb the stored value during read (read disturb issue).In 8T/10T, read decoupling ensures the internal node isn't affected during read, enabling higher SNM.Must be fast and low-power, as sense amplifiers consume significant dynamic power.Mismatch due to variation must be accounted for in sizing. May need offset cancellation or calibration in advanced nodes.

### 4. Performance Analyzer

This block captures and analyzes the key performance metrics of each SRAM cell design under the same conditions.Power Consumption:Static Power: Due to leakage (subthreshold and gate leakage).Dynamic Power: Due to bitline charging/discharging, switching activity.Static Noise Margin (SNM):Indicates stability of the cell. Higher SNM  $\rightarrow$  better immunity to noise.Read SNM: Stability during read. Critical for 6T.Write SNM: Ability to flip the state. Improved in 10T via writeassist.Area:Physical layout size ( $\mu m^2$  per bit).

# **3.SYSTEM ARCHITECTURE**

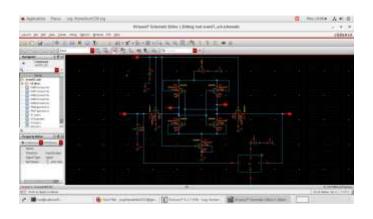

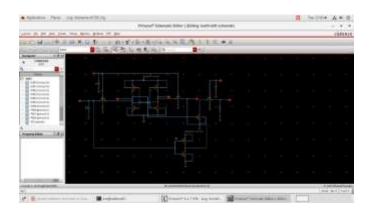

In **Block 1** (**SRAM Cell Design**), three SRAM cell architectures—6T, 8T, and 10T—are implemented at the transistor level using Virtuoso's schematic editor. The 6T cell consists of six transistors forming two cross-coupled inverters and two access transistors. The 8T and 10T cells enhance stability by decoupling the read and write paths, with the 10T variant offering even stronger isolation at the cost of area and complexity.

**Block 2 (Technology Specification)** involves setting the design environment to use a 45nm technology node. Standard CMOS process parameters are configured, including a supply voltage of 1.0V and appropriate transistor sizing. Design corners such as TT, SS, and FF are applied to analyze variability under different

manufacturing conditions, and temperature variations are introduced to examine thermal robustness

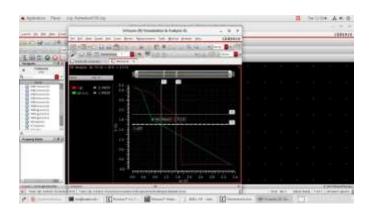

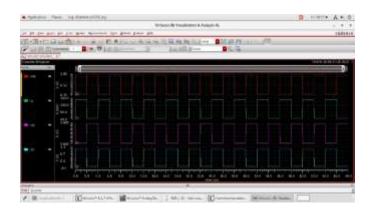

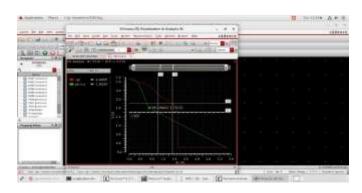

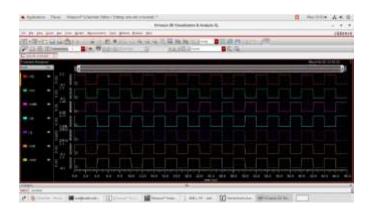

In **Block 3** (Simulation Setup), Virtuoso's ADE XL/Explorer is used to conduct a series of simulations. Transient simulations are used to observe write and read operations, while DC simulations generate butterfly curves to measure Static Noise Margin (SNM). Monte Carlo simulations are employed to understand the impact of process variations on performance. The simulation environment also captures delay, dynamic power, and leakage currents.

**Block 4 (Performance Metrics)** focuses on evaluating and comparing key performance parameters. The 6T SRAM cell, while compact, shows moderate SNM and limited write margins. The 8T cell improves read stability due to read-path isolation, making it suitable for read-intensive applications. The 10T cell offers the highest noise margins and robustness but at the expense of increased area and power. Metrics such as read/write SNM, access time, dynamic and leakage power, and cell area are analyzed comprehensively.

**Block 5 (Layout & Post-Layout Simulation)** extends the analysis by creating the physical layout of each SRAM cell using Virtuoso Layout Editor. Design Rule Checks (DRC) and Layout Versus Schematic (LVS) checks ensure correctness. The layout is followed by parasitic extraction, and post-layout simulations are performed to observe the effects of interconnect delays and capacitance on the performance metrics, giving a more realistic view of the SRAM behavior.

Finally, **Block 6** (**Result Analysis & Conclusion**) compiles the simulation data into comparative graphs and tables. It concludes that while 6T is area-efficient, 8T provides a good trade-off between stability and size, and 10T is optimal for high-reliability memory but consumes more resources. The analysis highlights how different SRAM topologies are better suited for different applications, such as low-power IoT devices, high-speed caches, or radiation-hardened systems.

# International Journal of Scientific Research in Engineering and Management (IJSREM)

SJIF Rating: 8.586

Volume: 09 Issue: 06 | June - 2025

RWL WBL WBL QWBLWBLBQWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWBLBWB

### Result

Run the above code, input the images shown in the image below and observe the live output.

### 6t sram:

### DC Analysis

Read Operation:

ISSN: 2582-3930

### 8t sram:

# DC Analysis:

# Read Operation:

### 10t sram:

© 2025, IJSREM | <u>www.ijsrem.com</u>

Ι

Volume: 09 Issue: 06 | June - 2025

SJIF Rating: 8.586

ISSN: 2582-3930

### **DC Analysis:**

### **4.CONCLUSION**

In this study, a structured and modular block diagram framework was proposed and utilized for the **comparative performance analysis of 6T, 8T, and 10T SRAM cells** in 45nm CMOS technology. Through this approach, key performance metrics—including **read/write delay**, **static noise margin (SNM)**, **power consumption**, and **area** were analyzed under consistent testing conditions.

The results of this analysis reveal that each SRAM topology offers distinct trade-offs:

- The **6T SRAM cell** is area-efficient and offers high speed, making it suitable for **high-density**, **high-speed cache applications**. However, it suffers from **reduced stability**, especially under low supply voltages or in the presence of process variations.

- The **8T SRAM cell** introduces read decoupling, significantly enhancing **read stability and noise margins** without modifying the core write mechanism. This makes it more **robust for lowpower and sub-threshold applications**, though it incurs moderate area and power overhead.

• The **10T SRAM cell**, with full read-write decoupling and write-assist features, provides the **highest reliability and robustness** among the three, especially under **aggressive voltage scaling and environmental stress**. It is ideal for **mission-critical and ultra-low-power applications**, albeit at the cost of increased area and complexity.

### ACKNOWLEDGEMENT.

We would like to express our sincere gratitude to our guide and faculty members for their invaluable support and guidance throughout the course of this project. We also thank our institution for providing the necessary resources and environment to carry out this research. Lastly, we appreciate the contributions of all team members whose dedication and collaboration made this project possible.

I deeply grateful to our esteemed faculty mentors, **Dr. Sonagiri China Venkateswarlu, Dr. V. Siva Nagaraju**, from the Department of Electronics and Communication Engineering at the Institute of Aeronautical Engineering (IARE).

Dr. Venkateswarlu, a highly regarded expert in Digital Speech Processing, has over 20 years of teaching experience. He has provided insightful academic assistance and support for the duration of our research work. Dr. Siva Nagaraju, an esteemed researcher in Microwave Engineering who has been teaching for over 21 years, has provided us very useful and constructive feedback, and encouragement which greatly assisted us in refining our technical approach.

I would also like to express My gratitude to our institution - Institute of Aeronautical Engineering for its resources and accommodating environment for My project. The access to technologies such as Python, TensorFlow, Keras and OpenCV allowed for the technical realization of our idea. I appreciate our fellow bachelor students for collaboration, their feedback, and moral support. Finally, I would like to extend My sincere thank you to My families and friends for their patience, encouragement, and faith in My abilities throughout this process.

### REFERENCES

1. Rukkumani. V, Devarajan N, "Design and Analysis of static random-access memory by Schmitt trigger topology for low voltage application," in Journal of Engineering Science

Volume: 09 Issue: 06 | June - 2025

SJIF Rating: 8.586

ISSN: 2582-3930

and Technology, Vol. 11, No. 12 (2016) 1722 -

2. Tomar. V K, Vinay Kumar, "A Comparative Performance Analysis of 6T, 7T and 8T SRAM Cells in 18nm FinFET Technology," in International Conference on Power Electronics and IoT Applications in Renewable Energy and its Control

(PARC), Mathura, India, 2020, pp. 329-333

3. D. Mittal and V. K. Tomar, "Performance Evaluation of 6T, 7T, 8T, and 9T SRAM cell Topologies at 90 nm Technology Node," in 2020 11th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Kharagpur, India, 2020, pp. 1-4. https://doi.org/10.1109/ICCCNT49239.2020.9225

<u>554</u>

4. Pinki Narah, Sharmila Nath, "A Comparative Analysis of SRAM Cells in 45nm, 65nm, 90nm Technology," in Int. Journal of Engineering Research and Application, Vol. 8, Issue5 (Part -I),

May 2018, pp31-36.

5. P. S. Grace and N. M. Sivamangai, "Design of 10T SRAM cell for high SNM and low power," in 2016 3rd International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 2016, pp. 281-285. https://doi.org/10.1109/ICDCSyst.2016.7570609

6. R. Kumar et al., "Design and Benchmark of Iso-Stable High Density 4T SRAM cells for 64MB arrays in 65nm LSTP," in 2020 IEEE 17th India Council International Conference (INDICON), New Delhi, India, 2020, pp. 1-7. https://doi.org/10.1109/INDICON49873.2020.934 2091

### BIOGRAPHIES

**BOLEM BHUMIKA** studying 3rd year department of Electronics And Communication Engineering at Institute Of Aeronautical Engineering ,Dundigal .She Published a

Research Paper Recently At IJSREM as a part of academics . She has a interest in IOT and VLSI.

Dr Sonagiri China Venkateswarlu professor in the Department of Electronics and Communication Engineering at the Institute of Aeronautical Engineering (IARE). He holds a Ph.D. degree in Electronics and Communication Engineering with a specialization in Digital Speech Processing. He has more than 40 citations and paper publications across various publishing platforms, and expertise in teaching subjects such as microprocessors and microcontrollers, digital signal processing, digital image processing, and speech processing. With 20 years of teaching experience, he can be contacted at email: c.venkateswarlu@iare.ac.in

**Dr. V. Siva Nagaraju** is a professor in the Department of Electronics and Communication Engineering at the Institute of Aeronautical Engineering (IARE). He holds a Ph.D. degree in Electronics and Communication Engineering with a specialization in Microwave Engineering. With over 21 years of academic experience, Dr. Nagaraju is known for his expertise in teaching core electronics subjects and has contributed significantly to the academic and research community. He can be contacted at email: <u>v.sivanagaraju@iare.ac.in</u>.