### POWER QUALITY ENHANCEMENT OF DIODE CLAMPED MULTILEVEL INVERTER USING 3RD HARMONIC INJECTION

Dr. Reeta Pawar<sup>1</sup>, Mr. Rajesh Kumar Vishwakarma<sup>2</sup>, Mr. Balwant Singh Parihar<sup>2</sup>

Professor<sup>1</sup>, Associate Professor<sup>2</sup> Electrical &Electronics Engineering Madhyanchal Professional University, Bhopal<sup>1,2,3</sup> <u>reetapawar2010@gmail.com<sup>1</sup></u>, <u>rjsh\_vishwakarma@yahoo.co.in<sup>2</sup></u> balwantparihar1012@gmail.com<sup>3</sup>

#### ABSTRACT

The concept of multilevel power conversion has been gaining popularity mainly due to improved power quality, lower switching losses, better electromagnetic compatibility, and higher voltage capability. These converters are suitable in highvoltage and high-power applications due to their ability to synthesize waveforms with better harmonic spectrum and attain higher voltages with limited maximum device rating. a These improvements in power conversion are achieved by using multiple voltage steps strategy which is an essential reason for medium voltage operation to lowering dv/dt and reducing stress on motor winding insulations. Multilevel power conversion has been receiving increasing attention in past few years for high power applications.

**Keywords**: -Variations in load, Multilevel inverters, Semiconductor Devices.

#### **1. INTRODUCTION**

Multilevel inverters are the class of inverters in which the output voltage waveform composed of number of levels of voltage typically obtained from the capacitor voltage sources. Researchers suggested various topologies of the multilevel inverters i.e DCMLI, FCMLI, CMLI etc. Apart from the advantages there are some inherent problems associated with different topologies of the multilevel inverter like capacitor voltage unbalance, common mode voltage generation, voltage drift problems with increased voltage levels, Neutral Point Potential Variation (3-Level Diode Clamped Inverter). Hence the possible research areas in multilevel inverters are Unequal Ratings of Switching Devices, Capacitor Voltage Unbalance, High Voltage Rating for Blocking Diodes, Optimized modulation strategy, Real Power Flow Control, Common mode voltage reduction, Optimization of a soft-switching circuit

with inductor coupling, Voltage drift problems with increased voltage levels, Transformer-less Distribution System, Use of Optical Fibers for Sensors and Controls, Use of Advanced High-Voltage, High-Power Semiconductor Devices, Unequal duty of individual device, Switching Losses. some research are based on the analysis and comparison of these topologies among themselves on the basis of their cost, number of switching devices, capacitors, diodes used in the circuit of same level, THD in the output voltage for the same level and the magnitude of the output voltage produced.

### 2. CONCEPT OF MULTILEVEL INVERTERS

Multilevel inverter includes an array of power semiconductor devices and capacitors voltage sources, the output of which generates voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitors voltages to obtain high- voltage at the output, while the power semiconductors have to withstand only reduced voltages. We can observe a two level inverter generates an output voltage with two values (levels) with respect to negative terminal of the capacitor. While three and level inverter generates three voltages, and a nine-level inverter generates a nine level output voltages. In all this cases devices are not arranged in series but they are arranged in such way that, they gain the capability to generate such kind of voltages.

Herein, we should remember one important thing i.e. as the number of steps increases in the output waveforms; harmonic content comes down. Thus power quality of such waveforms will increase drastically. However, in order to generate step kind of waveforms in output side, different Multilevel based archetypes are successfully built and verified. But general principle of multilevel inverters is the synthesis of the AC voltage from several different voltage levels on the DC bus. As the number of voltage levels on the input DC side increases, the output voltage adds more steps which approach the sinusoidal wave.

## 2.1 2-LEVEL AND 3-LEVEL VOLTAGE SOURCE INVERTERS

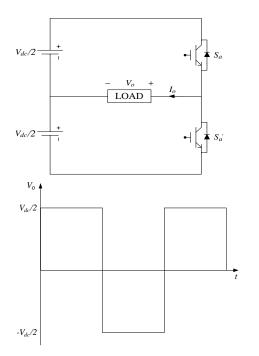

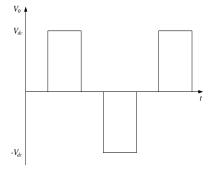

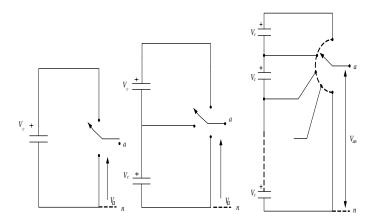

A 2-level voltage source inverter, also known as half-bridge inverter is depicted in Figure 2.1.1 S1and S2 are the two power switches which are AC activated for equal intervals to generate a 2level square wave output waveform. Both S1 and S2operate in strict complement sense so as to avoid the short circuit across the DC voltage source. Output voltage levels with corresponding switch states are given in table 2.1.1 The structure of a 3-level voltage source inverter, also known as full-bridge inverter or H-bridge inverter along with its output is shown in Figure 2.1.2 It employs four power switches S1, S2, S3 and S4. Similar to the half-bridge inverter, S1 and S3 operate in strict complement sense to avoid short circuit across the DC voltage source. Same is the case for switches S2 and S4. Table 2.1.2 explains how power

switches in full-bridge inverter are activated.

$V_{dc} \xrightarrow{+} I_{o} \xrightarrow{+} V_{o} \xrightarrow{-} I_{o} \xrightarrow{+} I_{O} \xrightarrow{-} I_{O} \xrightarrow{+} I_{O} \xrightarrow{$

Figure 2.1.1 half bridge inverter and its output

### Table 2.1.1 Switching Pattern of a Half-BridgeInverter

| ON s                  | state | Output              |  |

|-----------------------|-------|---------------------|--|

|                       | State | voltage             |  |

| switch                |       | $V_o$               |  |

| <b>S</b> <sub>1</sub> |       | $+V_{DC}/2$         |  |

| <b>S</b> <sub>2</sub> |       | -V <sub>DC</sub> /2 |  |

Figure 2.1.2 Full bridge inverter

# Table 2.1.2 Switching Pattern of a Full-BridgeInverter

| ON state<br>switch<br>pairs                   | Output<br>voltage V <sub>o</sub> |

|-----------------------------------------------|----------------------------------|

| $S_1, S_2$                                    | $+V_{DC}$                        |

| <b>S</b> <sub>3</sub> , <b>S</b> <sub>4</sub> | -V <sub>DC</sub>                 |

Inverters employing 2-level waveform are rarely used in practice due to presence of relatively large 3<sup>rd</sup> and 5<sup>th</sup> order harmonics and high dv/dt stress. Although a 3-level waveform is better than a 2level waveform and can be used for household applications like uninterruptible power supplies

Τ

(UPS), still there is significant presence of lower order harmonics which can cause reduction in efficiency of the circuit. As an alternative to these issues, multilevel voltage source inverters were introduced.

#### **2.2 MULTILEVEL INVERTERS**

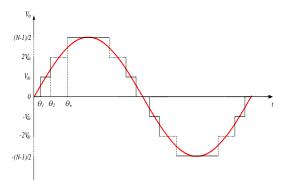

Multilevel inverters are recognized by their stepped output waveform. The generalized stepped waveform for a single-phase *N*-level multilevel inverter is shown in Figure 3.3 The waveform is composed of equal positive and negative halves of (N-1)/2 voltage levels wherein a sine wave can be approximated as shown.

Figure 2.2.1 Generalized stepped waveform of multilevel inverters

#### **2.3 MULTILEVEL INVERTERS**

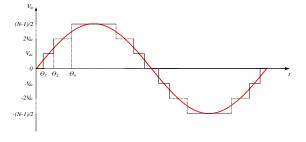

Multilevel inverters are recognized by their stepped output waveform. The generalized stepped waveform for a single-phase *N*-level multilevel inverter is shown in Figure 2.3.1 The waveform is composed of equal positive and negative halves of (N-1)/2 voltage levels wherein a sine wave can be approximated as shown.

Figure 2.3.1 Generalized stepped waveform of multilevel inverters

### 2.4 MULTILEVEL INVERTER STRUCTURES

Three different major multilevel converter structures have been applied in industrial applications: cascaded H-bridges converter with separate DC sources, diode clamped, and flying capacitors

Figure 2.4.1 one phase leg of an inverter with (a) two levels, (b) three levels, and (c) n levels

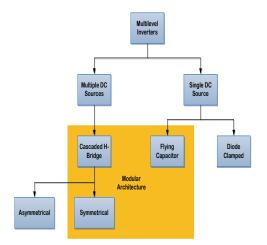

## 2.5 CLASSIFICATION OF MULTILEVEL INVERTERS

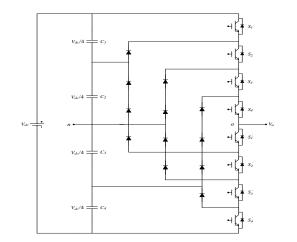

Figure 2.6.1 5-level Diode-clamped inverter

Figure 2.5.1 Multilevel inverter classifications

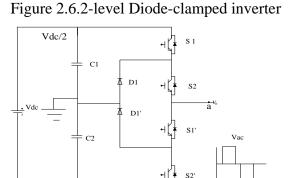

### 2.6 DIODE CLAMPED MULTILEVEL INVERTER

Diode-clamped multilevel inverter is the name given to neutral-point clamped PWM inverter extended to higher number of levels [3, 4]. The diode-clamped multilevel inverter has found wide acceptance for its capability of high voltage and high efficiency operation. Figure 3.6

# Table 2.6.1 Switching Pattern of Diode-Clamped Multilevel Inverter

| Output                                      | Switch states |                |            |            |     |     |     |                         |

|---------------------------------------------|---------------|----------------|------------|------------|-----|-----|-----|-------------------------|

| Voltage                                     | S1            | S <sub>2</sub> | <b>S</b> 3 | <b>S</b> 4 | S1' | S2' | S3' | <b>S</b> 4 <sup>′</sup> |

| $\mathbf{V}_{0} = \mathbf{V}_{\mathbf{an}}$ | 51            | 52             | 03         | 04         | 51  | 02  | 05  | 04                      |

| V <sub>DC</sub> /2                          | 1             | 1              | 1          | 1          | 0   | 0   | 0   | 0                       |

| $V_{DC}/4$                                  | 0             | 1              | 1          | 1          | 1   | 0   | 0   | 0                       |

| 0                                           | 0             | 0              | 1          | 1          | 1   | 1   | 0   | 0                       |

| -V <sub>DC</sub> /4                         | 0             | 0              | 0          | 1          | 1   | 1   | 1   | 0                       |

| V <sub>DC</sub> /2                          | 0             | 0              | 0          | 0          | 1   | 1   | 1   | 1                       |

Τ

### Table-2.6.2 Switching States In One Leg of the

| <b>Three-Level Diode</b> | Clamped Inverter |

|--------------------------|------------------|

|--------------------------|------------------|

| Switch status                                  | state                               | Pole voltage          |

|------------------------------------------------|-------------------------------------|-----------------------|

| $S_1 = on, S_2 =$                              | S = +ve                             | $V_{ao} = V_{DC/2}$   |

|                                                | $\mathbf{D} = \mathbf{V}\mathbf{C}$ | • a0- • DC /2         |

| on                                             |                                     |                       |

| $S_1 = off, S_2 =$                             |                                     |                       |

| off                                            |                                     |                       |

| $\mathbf{S}_1 = \mathrm{off},  \mathbf{S}_2 =$ | <b>S</b> = 0                        | $V_{ao} = 0$          |

| on                                             |                                     |                       |

| $\mathbf{S}_1 = \mathbf{on},  \mathbf{S}_2 =$  |                                     |                       |

| off                                            |                                     |                       |

| $\mathbf{S}_1 = \mathbf{off},  \mathbf{S}_2 =$ | S = +ve                             | $V_{ao} = - V_{DC/2}$ |

| off                                            |                                     |                       |

| $S_1 = on$ , $S_2 =$                           |                                     |                       |

| on                                             |                                     |                       |

Table-2.6.3 Switching States In One Leg of theThree-Level Diode Clamped Inverter

| Switch status                                  | state            | Pole              |

|------------------------------------------------|------------------|-------------------|

|                                                |                  | voltage           |

| $S_1 = on$ , $S_2 =$                           | S = +ve          | V <sub>ao</sub> = |

| on                                             |                  | $V_{DC/2}$        |

| $S_1 = off, S_2 =$                             |                  |                   |

| off                                            |                  |                   |

| $\mathbf{S}_1 = \mathrm{off},  \mathbf{S}_2 =$ | $\mathbf{S} = 0$ | $V_{ao} = 0$      |

| on                                             |                  |                   |

| $S_1 = on$ , $S_2 =$                           |                  |                   |

| off                                            |                  |                   |

| $\mathbf{S}_1 = \mathrm{off},  \mathbf{S}_2 =$ | S = +ve          | $V_{ao}$ = -      |

| off                                            |                  | $V_{DC/2}$        |

| $S_1 = on, S_2 =$                              |                  |                   |

| on                                             |                  |                   |

#### **3. CONCLUSION**

-Vdc/2

The diode-clamped inverter provides multiple voltage levels through connection of the phases to a series of capacitors. The concept can be extended to any number of levels by increasing the number of capacitors. Early descriptions of this topology were limited to three-levels where two capacitors are connected across the DC bus resulting in one additional level. The additional level was the neutral point of the DC bus. However, with an even number of voltage levels, the neutral point is not accessible, and the term multiple point clamped (MPC) is sometimes applied. Due to capacitors voltage balancing issues, the diode-clamped inverter implementation has been limited to three level. Because of industrial developments over the past several years, the three level inverter is now used extensively in industrial application.

T

#### REFERENCES

- Pregelj, A.; Begovic, M.; Rohatgi, A.

"Impact of inverter configuration on PV system reliability and energy production," Photovoltaic Specialists Conference, 2002. Conference Record of the Twenty-Ninth IEEE, vol., no., pp. 1388-1391, 19-24 May 2002

- [2] Jih-Sheng Lai; Fang ZhengPeng;

"Multilevel converters-a new breed of power converters," Industry Applications Conference, 1995. Thirtieth IAS Annual Meeting, IAS '95., Conference Record of the 1995 IEEE, vol.3, no., pp.2348-2356 vol.3, 8-12 Oct 1995.

- [3] Rodriguez, J.; Jih-Sheng Lai; Fang ZhengPeng; "Multilevel inverters: a survey of topologies, controls, and applications," Industrial Electronics, IEEE Transactions on, vol.49, no.4, pp. 724- 738, Aug 2002.

- [4] Rodriguez, J.; Franquelo, L.G.; Kouro, S.; Leon, J.I.; Portillo, R.C.; Prats, M.A.M.; Perez, M.A.; , "Multilevel Converters: An Enabling Technology for High-Power Applications," Proceedings of the IEEE , vol.97, no.11, pp.1786-1817, Nov. 2009.

- [5] Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A. "A Survey on Cascaded Multilevel Inverters," Industrial Electronics, IEEE Transactions on, vol.57, no.7, pp.2197-2206, July 2010.

- [6] Panagis, P.; Stergiopoulos, F.; Marabeas,

P.; Manias, S. "Comparison of state of the art multilevel inverters," Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, vol., no., pp.4296-4301, 15-19 June 2008.

- [7] Tolbert, L.M.; Fang ZhengPeng; Habetler, T.G. "Multilevel converters for large electric drives," Industry Applications, IEEE Transactions on, vol.35, no.1, pp.36-44, Jan/Feb 1999.

- [8] Fang ZhengPeng; , "A generalized multilevel inverter topology with self voltage balancing," Industry Applications, IEEE Transactions on, vol.37, no.2, pp.611-618, Mar/Apr 2001.

- [9] Teodorescu, R.; Blaabjerg, F.; Pedersen, J.K.; Enjeti, P.N.; , "Multilevel inverter by cascad VSI," Industrial Electronics, IEEE Trans vol.49, no.4, pp. 832- 838, Aug 2002.

- [10] Nabae, Akira; Takahashi, Isao; Akagi, Hirofumi; , "A New Neutral-Point-Clamped PWM Inverter," Industry Applications, IEEE Transactions on , vol.IA-17, no.5, pp.518-523, Sept. 1981

- [11] T. A. Meynard and H. Foch, "Multi-level choppers for high voltage applications," in Proc. Eur. Conf. Power Electron. Appl., 1992, vol. 2, pp. 45–50.

- [12] M. Marchesoni, M. Mazzucchelli, and S. Tenconi, "A non-conventional power converter for plasma stabilization," in Proc. Power Electron. Spec. Conf., 1988, pp.

L

122-129.

- [13] De, S.; Banerjee, D.; Siva Kumar, K.;

Gopakumar, K.; Ramchand, R.; Patel, C.; ,

"Multilevel inverters for low-power application," Power Electronics, IET , vol.4, no.4, pp.384-392, April 2011.

- [14] Liu, Y.; Luo, F.L. "Multilevel inverter with the ability of self voltage balancing," Electric Power Applications, IEE Proceedings - , vol.153, no.1, pp. 105- 115, 1 Jan. 2006.

- [15] A. Rufer, M. Veenstra, and K. Gopakumar,

"Asymmetric Multilevel Converter for

HighResolution Voltage Phasor

Generation", in Proceedings of the

European Power Electronics and

Applications Conference (EPE 1999), 1999

Τ