## **Review Paper on Multioperand Adder**

Laxmi Pardhi M.Tech.Student Priyadarshini college of Engineering, Hingna,India Sharda Mungale Assistant Professor Priyadarshini college of Engineering, Hingna,India

**Abstract :** In this paper,Ripple carry adder and Wallace carry adder are designed,encoded in verilog and simulated in xilinx software.This peper presents the pertinent choice for selecting the adder topology with the trade off between delay,power consumption and area.

**Keywords** : Ripple carry adder and Wallace tree adder.

## **Introduction :**

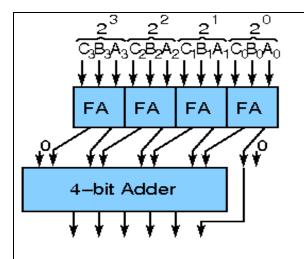

Multi operand adders usually consists of compression trees which reduced the number of operands per a bit to two, and a carry-propagate for the two operands in ASIC implementation.

A method to compute the exact number of carry bits required for a multi-operand addition operation. A fast combinatorial parallel 4-operand adder module is presented.

The area, delay and energy efficiency of the BTA depends on the performance of adders. Which can be used to develop the BTA structure, where each

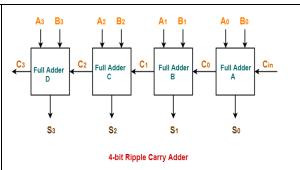

length numbers, it is however not very efficient when large bit numbers are used. One of the most serious drawbacks of this adder is that the delay increases linearly with the bit length. The worst-case delay of the RCA is when a carry signal transition ripples through all stages of adder chain from the least significant bit to the most significant bit, which is approximated by:

t = (n - 1) t c + t s....Eq (1)

where t c is the delay through the carry stage of a full adder, and t s is the delay to compute thesum of the last stage. The delay of ripple carry adder is linearly proportional to n, the number of bits, therefore the performance of the RCA is limited when n grows bigger. The advantages of the RCA are lower power consumption as well as compact layout giving smaller

chip area. The design schematic of RCA is shown in Figure

International Journal of Scientific Research in Engineering and Management (IJSREM) Volume: 06 Issue: 12 | December – 2022 Impact Factor: 7.185 ISSN: 2582-3930

adder has its own tradeoffs between area, delay and energy consumption.

Ripple carry adder The ripple carry adder is constructed by cascading full adders (FA) blocks in series. One full adder is responsible for the addition of two binary digits at any stage of the ripple carry. The carryout of one stage is fed directly to the carry-in of the next stage. Even though this is a simple adder and can be used to add unrestricted bit length of length (k+log2n-1). Since each CSA reduces three inpu operands to two output operands, the heighth(n) of a Wallace tree forninputs follows the recurrence relation:

h(n)=1+h([2n/3])

By removing the ceiling operator, we obtain a lower bound for the treeheight:

$h(n) \ge log 1.5(n/2)$

Conversely, the maximum number of inputsn(h) that can be added by aWallace tree of heighthis:

$$n(h) = [3n(h-1)/2]$$

Multi-Operand Addition13which leads to the lower bound,

$$n(h) \ge 2(3/2)h-1$$

## Wallace tree adder

When CSA units are used to combine rows of bits as early as possible in the tree, a Wallace Tree is obtained. At every level of Figure 6, foreach column of three dots, a full-adder combines them. The bit Wallace tree with inputs reduces it input bits to two bits Vector minimisation. The comparison result shows that the proposed RCA design offers better efficiency in terms of area, delay and energy than the existing RCA. Using this RCA design, the BTA structure is proposed. The synthesis result reveals that the proposed 320perand BTA provides the saving of 22.5% in area-delay product and 28.7% in energy delay product over the recent Wallace tree

adder which is the best among available multi-operand adders. The synthesis result shows that the performance of multiplier designs improved significantly due to the use of proposed BTA. Therefore, the proposed BTA design can be a better choice to develop the area, delay and energy efficient digital International Journal of Scientific Research in Engineering and Management (IJSREM) Volume: 06 Issue: 12 | December – 2022 Impact Factor: 7.185 ISSN: 2582-3930

## Objective

1.Objective of this is to implement and synthesize a ripple carry and wallace tree adder.

2.Comparing both ripple carry adder and wallace tree adder for area, delay and energy.

3.By synthesized in xilinx FPGA in presence of verilog VHDL.

1.Sujit Patil, Subodh kumar singhal, "Area delay and energy efficient multi operand binary tree adder", June 2020...,pp. 588-593In this, the critical path of ripple carry adder (RCA)-based binary tree adder (BTA) is analysed to find the possibilities for delay designed by sharing the CBL term; the

transistor count in this CSA can be decreased to a great extent. Moreover, the power consumption and delay also reduced at a great extent. The

systems for signal and image processing applications.

2.R.UMA, Vidya Vijayan, M.Mohanpriya, Paul, Sharon "Area, delay and power of comparison adder topologies", fefruary2012..., pp. 153-168. In this, it presents the pertinent choice for selecting the adder topology with the tradeoff between delay, power consumption and area. The adder topology used in this work are ripple carry adder, carry look-ahead adder, carry skip adder, carry select adder, carry increment adder, carry save adder and carry bypass adder. The module functionality and performance issues like area, power dissipation and propagation delay are analyzed at 0.12µm 6metal layer CMOS technology using microwind tool.

3.Rajwinder kaur, Amit Grover, Vishal Sharma, "An Efficient Carry Select Adder Design by using different Topologies", July2015..pp.24-27.

In this, CSA has been compared using 45nm, 90nm and 180nm technologies. It is concluded that, the results are calculated with different widths of NMOS & PMOS. It is

for low power and high speed ripple carry

suggested design technique has been applied for the implementation of 1-bit CSA adder and simulation results verified its proficiency.

4.Sakshi Sharma 1 , Pallavi Thakur,"Design of High Speed Power Efficient Wallace Tree Adders",May 2016, pg. 18-22.

In this paper FIFB, FIEB and FISB Carry Save Adders and Wallace Tree Adders are designed, encoded in Verilog and simulated using Cadence Software. The 180nm CMOS technology is used for implementation of adders. The simulation results are compared for power consumption, delay, silicon area and dynamic power dissipation. As the length of inputs increase, power dissipated, silicon area and delay increase in both Carry Save Adder and Wallace Tree Adder. Compared to traditional CSA, the proposed Wallace Tree Adder is found to have shorter delay, lesser power dissipation and lesser silicon area and hence more cost efficient and a better option for real-time applications.

5.Kokila Bharti Jaiswal 1 , Nithish Kumar V 1,Pavithra Seshadri 2 and Lakshminarayanan G 1 "Low Power Wallace Tree Multiplier Using Modified Full Adder", 2015 In applications such as Digital Signal Processing adder featuring Gate Diffusion Input (GDI) structure and Hybrid CMOS logic style. The hybrid logic style is employed in order to achieve a wide range of applications. The Gate-Diffusion-Input Multiplexer full adder (GDI-MUX) design eliminates the need of XORIXNOR gates for designing full adder cell. The performance parameters such as area, delay, power and Power-Delay-Product (PDP) were analyzed using SPICE.

6.S. Archana, G. Durga,"Design of Low Power and High Speed Ripple

Carry Adder", April 3-5, 2014, India

In applications such as Digital Signal Processing architecture, microprocessor and microcontroller, full adder circuit plays an important role. Performance criteria for the logic styles are circuit speed, area and power dissipation. The major goal that requires ultimate attention is power consumption. Hence adders are designed in such a way to

Reduce the propagation delay which is also a cause for power consumption. Here two new designs adopted for low power and high speed ripple carry adder featuring Gate Diffusion Input (GDI) structure and Hybrid CMOS logic style. The hybrid logic style is

| architecture,microprocessor and                    | employed in order to achieve a wide range of  |

|----------------------------------------------------|-----------------------------------------------|

| microcontroller,full adder circuit plays an        | applications.The Gate-Diffusion-Input         |

| important role. Performance criteria for the logic | Multiplexer full adder (GDI-MUX) design       |

| styles are circuit speed, area and power           | eliminates the need of XOR1XNOR gates for     |

| dissipation. The major goal that requires ultimate | designing full adder cell. The performance    |

| attention is power consumption.Hence adders are    | parameters such as area, delay, power and     |

| designed in such a way to reduce the propagation   | Power-Delay-Product (PDP) were analyzed       |

| delay which is also a cause for power              | using SPICE.                                  |

| consumption.Here two new designs adopted           |                                               |

|                                                    | 4.R.UMA, Vidya Vijayan, M.Mohanpriya,         |

| Implementation and synthesis of Ripple carry       | Sharon Paul, "Area,delay and power            |

| adder.                                             | comparison of adder                           |

| Implementation and synthsis of Wallace tree        | topologies",fefruary2012,pp. 153-168.         |

| adder.                                             |                                               |

| Comparison of Ripple carry adder and Wallace       | 5.Rajwinder kaur, Amit Grover, Vishal Sharma, |

| tree adder for area, delay and energy.             | "An Efficient Carry Select Adder Design by    |

|                                                    | using different Topologies",                  |

| Result.                                            | July2015pp.24-27.                             |

| Reference                                          |                                               |

| 1.Sujit Patil, Subodh kumar singhal, "Area delay   | 6.S. Archana, G. Durga,"Design of Low Power   |

| and energy efficient multi operand binary tree     | and High Speed Ripple                         |

| adder", June 2020,pp. 588-593                      | Carry Adder", April 3-5, 2014, India          |

|                                                    |                                               |

| 2. Sakshi Sharma 1 , Pallavi Thakur,"Design of     |                                               |

| High Speed Power Efficient Wallace Tree            |                                               |

| Adders", May 2016, pg. 18-22.                      |                                               |

|                                                    |                                               |

| 3.Kokila Bharti Jaiswal 1 , Nithish Kumar V        |                                               |

| 1,Pavithra Seshadri 2 and Lakshminarayanan G 1 |

|------------------------------------------------|

| "Low Power Wallace Tree Multiplier Using       |

| Modified Full Adder", 2015                     |

|                                                |

|                                                |

|                                                |

|                                                |