# Roba Multiplier: A Rounding-Based Approximate Multiplier for high-speed energy-efficient DSP

Dr.V.Raju Asst.Prof., Dept of ECE,

# **ABSTRACT**

In this work, we offer similar speeds but with energy efficiency. This approach is to fit closer to the closest momentum of two. An important part of the computer, so the removal is removed, accelerated and consumed at a small error rate. The proposed approach applies both signing and neglect. We provide three hardware implementations of approximate coefficients that exclude signing and signing for both operations. The effect of the estimated coefficients is evaluated by comparing its efficiency with the exact and exact conditions using different design parameters. In addition, analog effects are seen in two image processing applications - sharp images.

## 1. INTRODUCTION

Minimizing energy is one of the critical layout necessities in maximum digital structures, particularly laptops such as smartphones, drugs and other devices. [1] It without a doubt needs this minimized with little impact (pace) [1]. Digital virtual Divisions (DSPs) are a key factor of these mobile devices for multimedia packages. The middle of these devices is the good judgment of the mathematics, wherein multiply has the biggest market proportion amongst all the working system mathematics DSP [2]. Many DSP servers use picture and video algorithms, which in the end are photographs or videos which can be designed for human use. This segment summarizes a number of the preceding paintings to your discipline of expediency. In [3], an approximate and approximate wide variety of approximations turned into proposed based on a way called BAM (BAM). Making use of a way of bringing BAM [3] to a normal Budh modifier, suggests commands at maximum [5].

Kulkarni et al. [6] Proximity proposed with a  $2 \times 2$  coefficient of building blocks have been saved incorrectly, with 31.8% of energy, -forty five.4% on an appropriate coefficients. The approximate 32-bit probes for processing expectation had been designed [7]. It is 20% quicker than the entire supplement with a opportunity of about 14%. In [8], it is often recommended that the patient be extra patient than the calculated end result, with the ideal excellent of distribution. At [9] two circuits four: 2 had been designed and analyzed to be used in DDR3 multipliers. In [10] proposed multiple a architecture (ACMA) which may be configured with a precision, tolerable error. To boom the productiveness of ACMA, use a method referred to as predictions of practices that work on an immoderate computation foundation. Likewise, Bhardwaj et al. [11] Describes the quantity of Wallaceous Tree (AWTM) timber.

#### 1.1. EXISTING APPROACH

Most of the approximate delayed procedures proposed formerly depend upon structural modifications or the reduction of the complexity of the precision. On this venture, we [12] advise comparable approximations via making simple operations. The distinction between our paintings and [12]

is that, even though both regulations are the equal for maximum non-signatories, the common error of the proposed method is smaller.

#### 1.2. PROPOSED APPROACH

Proposed approximate coefficients within the place have been created with the aid of converting the conventional technique to multiplying the algorithms by using accepting enter values. We name this example of possibility coefficients (RoBA). The proposed multiplication approach is relevant to signed and non-essentials, wherein three great architectures are displayed.

## 2. METHODOLOGY

The motive of this mission is to describe the laptop mathematics scheme that uses two indicators in multiplication and department. The logarithms used within the arithmetic are similar to the real logarithm; due to the merger, there may be mistakes inside the overall performance of the transactions that use them. one evaluation could be accomplished to decide the most error which could end result from an estimate.

#### 2.1. APPROXIMATE COMPUTING

#### APPROXIMATE ADDERS

In this segment, we discuss techniques for approximate arrangement. We use RCAs and CSAs all through our concurrent dialogue in all regions.

#### A .Combination Of Glass Strategy

In this section, we describe the stairs for the cellular arrival of MAs, with fewer transistors. leaving behind a series of linked transistors will facilitate the storage / garage potential of the node. additionally, reducing pressure by means of casting off transistors also reduces the AC (switching capacity) to expose dynamic strength Pdynamic =  $\alpha$ CV 2DDf, in which one is the transfer movement or the common variety of changes exchanged per unit time and C is the storage capacitance charged with problem / problem. This results in much less strength dissipation. The decline inside the area is due to this manner. Now let's focus on the everyday governance of the Ministry of commerce with the abbreviation.

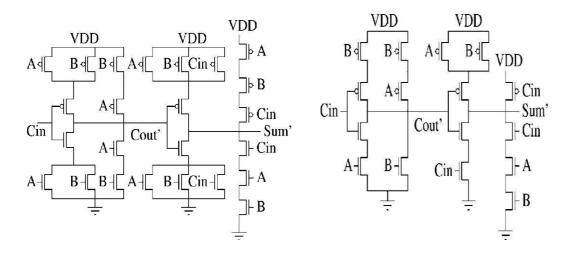

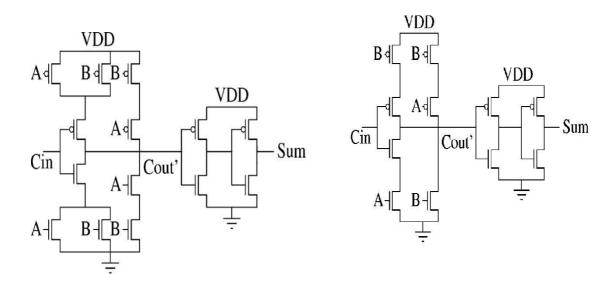

- 1) MA ordinary: figure 6 suggests the transistor degree plan of the conventional MA, which is known to deal with the FA. It has a total of 24 transistors, due to the fact the deployment isn't always based at the CMOS good judgment addition, it offers the identical ideal design in line with the removal of the chosen transistor.

- 2) Unification 1: To achieve MA with a smaller transistor, we begin to take transistors out of the traditional circuit one by one. however, we must now not do this in any manner. We want to ensure the combination of A, B and Cin will no longer cause quick circuits or circuits to open in an smooth circuit. some other important criterion is that accessibility is provided with the minimal blunders within the FA desk.

Approximate 2: The FA desk indicates that sum = Cout1 for 6 of 8 instances, except for combinations A = 0, B = 0, Cin = zero and A = 1, 1. Now within the everyday MA, *Cout* is calculated within the first step. So a simple way to get a easy scheme is to set Sum = Cout. but, we enter a buffer step after *Cout* (see figure 8) to get the identical feature.

ISSN: 2582-3930

Approximate 3: greater comfort can be completed by means of approximate equivalents 1 and 2. notice that this is the end result of the Cout errors and the 3 mistakes proven in desk I.

Approach 4: In-depth commentary of the FA table indicates that Cout = A for 6 of eight instances. in reality, Cout = B for 6 of 8 instances. due to the fact A and B have modified, we recollect cout = A, so we provide 4 estimates in which we simply use Inverter with an enter for the calculation Cout and the sum is calculated much like the estimate 1. Approach 5: If we need to make an independent sum of Cin, we have two options, Sum = A and Sum = B. So we've got options for approximate five: Sum = A, Cout = A and Sum = B, Cout = A and Cout = A and

Fig. 3.6. (a) Conventional MA. (b) MA approximation

Fig. 3.8. (a) MA approximation 2. (b) MA approximation 3.

The region reduction is in addition supported thru this method. We currently allow us to cognizance on the use of the MA often.

1) MA normal: determine 6 suggest the transistor sample of the normal MA transistor, which is identified by using the FA. There are 24 protocols. Considering this practice does now not depend on the applicable

ISSN: 2582-3930

Volume: 06 Issue: 02 | Feb - 2022

CMOS purpose, it gives a decent possibility to designate the shape this is assumed via the chosen transistor expulsion.

- 2) About 1: Given the remaining intention of acquiring a diploma of accuracy with a smaller transistor, we've started to squeeze a regular circuit transistor separately. But, we have to now not do that in our own form. We have to make certain that any information of mixtures A, B and Cin will now not create brief circuits or open circuits in hooked up circuits. Every other crucial step is that the following improvement ought to make a small mistake within the FA's table of reality.

- 3) Approximately 2: The table of FA truths shows the quantity = Cout1 for 6 of eight cases, except the combination of the elements = zero, B = zero, CIN = zero and A = 1, 1. in the mean time, in ordinary grasp, Cout seems inside the foremost organisation. Therefore, a particular method to get a forestall scheme is to set Sum = cout. in any case, we show the assist that has been set up after Cout (see parent eight) to create this type of application.

- 4) Approx. three: an extra regeneration may be acquired by approximate 1 and a pair of note that it generates a cout errors and three errors as shown in table 1.

- 5) Reunification 4: The overview of the FA's desk of truth suggests that Cout = A for 6 of eight cases. virtually, Cout = B for six of eight instances. Considering A and B have modified, we do not forget cout = those lines provide 4 hints wherein we handiest use Inverter with the input of the cout and the sum is calculated as points 1.

## 3. RESULTS AND DISCUSSION

To evaluate the effect of multiplier attributes, which are comparisons with a substantial and as well as accurate quantities. Baugh Woolley is based totally at the Wallace Tree structure (which has been signed), and Wails (the incorrect signature) has been decided on more than one times also, for similar postpone cases, DSM8 [16], DRUM6 [17] and PPATH[18] have been decided because [12] did no longer provide hardware overall performance.

Multiplication is performed the use of the language verilog for hardware description, after which synthesized using the Synopsys compiler, with the least not on time synthesis technology in forty five nm technology [14]. Then, the multi-care layout parameters are taken under consideration the usage of the Cadence chip system, these layout parameters of multiples are proven in desk 4.1. In nm technology, whilst the frequency is chosen by means of the pronounced not on time for every coefficient (see desk VI). The consequences show that the slowdown of strength and EDP is U-RoBA, at the same time as the DSM8 has the pleasant power intake and DRUM8 has the minimum size and PDA. The power postpone and U-RoBA's EDP are approximately 22% (15%), five% (thirteen%) and 26% (25%) lower than DSM8 (DRUM6).

ISSN: 2582-3930

Volume: 06 Issue: 02 | Feb - 2022

|             | Delay |       | Power |       | Arca  |       | Energy |       | EDP     |       | PDA      |       |

|-------------|-------|-------|-------|-------|-------|-------|--------|-------|---------|-------|----------|-------|

|             | (ns)  | Ratio | (mW)  | Ratio | (µm2) | Ratio | (pJ)   | Ratio | (ns×pJ) | Ratio | (pJ×µm2) | Ratio |

| U-RoBA      | 1.12  | 1.00  | 5.37  | 1.23  | 13224 | 2.32  | 6.0    | 1.00  | 6.7     | 1.00  | 79534    | 2.03  |

| S-RoBA      | 1.78  | 1.59  | 9.21  | 2.10  | 22800 | 4.00  | 16.4   | 2.73  | 29.2    | 4.33  | 373779   | 9.53  |

| AS-RoBA     | 1.37  | 1.22  | 7.6   | 1.74  | 14161 | 2.48  | 10.4   | 1.73  | 14.3    | 2.12  | 147444   | 3.76  |

| DSM8        | 1.44  | 1.29  | 4.38  | 1.00  | 8742  | 1.53  | 6.3    | 1.05  | 9.1     | 1.35  | 55138    | 1.41  |

| DRUM6       | 1.31  | 1.17  | 5.25  | 1.20  | 5700  | 1.00  | 6.9    | 1.14  | 9.0     | 1.34  | 39202    | 1.00  |

| HAAM        | 2.95  | 2.63  | 17.58 | 4.01  | 23194 | 4.07  | 51.9   | 8.62  | 153.0   | 22.71 | 1202864  | 30.68 |

| Wallace     | 1.69  | 1.51  | 17.3  | 3.95  | 33124 | 5.81  | 29.2   | 4.86  | 49.4    | 7.34  | 968446   | 24.70 |

| Baugh Wooly | 1.72  | 1.54  | 17.42 | 3.98  | 33306 | 5.84  | 30.0   | 4.98  | 51.5    | 7.65  | 997928   | 25.46 |

Table 4.1: Post layout design parameters of different 32-bit multiplier designs

|         |       | Sign Detector | Rounding | Shifter | Adder | Subtractor | Sign Set |

|---------|-------|---------------|----------|---------|-------|------------|----------|

| AS-RoBA | Power | 7.3%          | 11.4%    | 40.1%   | 29.9% | 7.1%       | 4.1%     |

|         | Delay | 3.8%          | 16.7%    | 34.8%   | 34.1% | 6.8%       | 3.8%     |

|         | Area  | 5.2%          | 9.0%     | 66.6%   | 13.7% | 3.9%       | 1.6%     |

| S-RoBA  | Power | 9.5%          | 5.5%     | 32.1%   | 16.6% | 8.0%       | 28.3%    |

|         | Delay | 15.5%         | 16.1%    | 23.8%   | 23.3% | 5.7%       | 15.5%    |

|         | Area  | 8.3%          | 6.6%     | 61.4%   | 11.7% | 3.9%       | 8.0%     |

Table 4.2: Breakdown of the power, delay, and area of AS-RoBA and S-RoBA

Conversely, the DSM8 (DRUM6) location (PDA) is ready 18% (fifty seven% and 51%) decrease. Override operation additionally leads to large layout parameters for S-RoBA and AS-RoBA compared to U-RoBA, DSM8 and DRUM6. Additionally, Hamma has the worst design parameters because of the array shape.

The outcomes also show that actual multiplier has a larger design parameter than those advised via U-RoBA and AS-RoBA. within the case of the S-RoBA multiplier, the delay is a mean of 3.4% extra than that of Baugh Wooley because of the use of actual terrible operations. similarly to the put off parameters, the other layout parameters of the S-RoBA multiplier are lots higher than the Bough Wooley multiplier. Alternatively, strength, area, energy, EDP and The S-RoBA PDA is ready forty seven%, 32%, forty five%, 43% and sixty three% decrease than the Bough Wooley multiplier. Cease of desk 4.2 shows the electricity output, delay, and the region of the AS-

Volume: 06 Issue: 02 | Feb - 2022

RoBA and S-RoBA devices various. As a result, the switch has a exquisite postpone, strength and floor postpone in multiplication gadgets.

| Device Utilization Summary                     |      |           |             |         |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|---------|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |  |  |  |  |

| Number of 4 input LUTs                         | 436  | 4,896     | 8%          |         |  |  |  |  |

| Number of occupied Slices                      | 225  | 2,448     | 9%          |         |  |  |  |  |

| Number of Slices containing only related logic | 225  | 225       | 100%        |         |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 225       | 0%          |         |  |  |  |  |

| Total Number of 4 input LUTs                   | 437  | 4,896     | 8%          |         |  |  |  |  |

| Number used as logic                           | 436  |           |             |         |  |  |  |  |

| Number used as a route-thru                    | 1    |           |             |         |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 32   | 158       | 20%         |         |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 2.78 |           |             |         |  |  |  |  |

## 4. CONCLUSION

On this mission, we've proposed an approximate pace multiplier, however the energy is referred to as the Roba coefficients. The high accuracy requested multiplier is primarily based at the enter inverse of the 2n access. This excludes the tremendous calculation of this multiplication through enhancing the velocity and electricity consumption at the fee of a small error.

The proposed approach is applicable to the signed and useless additives, three hardware implementations of approximate coefficients, which include one for the unigned and for signed transactions, had been discussed. The cautioned a couple of consequences are evaluated by comparing them with some of approximate and approximate uses of different layout parameters. The results show that, in most cases (all), the RoH multiplier structure exceeds the approximate number (absolute). Additionally, the effectiveness of advised approximate processes is investigated in two picture processing and clean software. Evaluation indicates the same photograph homes because the number of real multiplication policies.

## 5. REFERENCES

- [1] Al-Ato "the lowest-electricity VLSI circuit layout was discovered and explained:" IEEE Trans. Circuit system. Me, ri. reports. fifty nine, no. 1, pp. three-29, 2012

- [2] V. Gupta, D. Mohapatra, A. Raghunathan and okay. Roy, "virtual Low digital signal Processing the usage of additional Predatory" IEEE Trans. Designed assist computer systems. Circuit machine., variety. 32, no. page 1 web page 124-137 January 2013

- [3] X.R. Mahdiani, A. Ahmadi, S. Faqhei and S. Lucas "incorrect laptop conduct Binding for effective software of VLSI software" IEEE Trans. Circuit gadget. Me, ri. reviews. fifty seven, no. Fourth, pages 850-862, April 2010

- [4] R. Venkatesan, A. Agarwal, ok. Roy and A. Raghunathan, "MACACO: Sampling and evaluation of Approximate Computational Plans" in Proc. Int. Conf. Assisted Calculator - November 2011, 667-673.

- [5] F. Farshchi M.Appici and S.Faharia are "New Approximate Coefficients for digital virtual Processing" in Proc. seventeenth. conferences. Calculate. Archit. bathe. device. (CADS), October 2013, pages 25-30.

- [6] P. Kulkarni, P. Gupta and M. Ercegovac, "The Accuracy of strength change with the blended structure" in Proc. 24 Int. Conf. VLSI design, January 2011, 346-351.

- [7] d. Cayley, B Ph. Philip and Stephen. US US Saravy "signed the binary variety multiplication quantity for arithmetic statistics" in Proc. Designed with the aid of an architect. Transmission procedure, 2009, pp. ninety seven-104.

- [8] KY Y. Kyaw, W. L. Goh and k. S. Yeo, "fast-paced software for tolerance requests" in Proc. IEEE Int. Conf. stable state Circuit tool (EDSSC), December 2010, pp. 1-4.

- [9] A.Momeni, J.Han, P.Montushi and F. Lombardi, "IEEE Transplantation Integration design and evaluation". Comput., Vol. sixty four, no. web page 4 page 984-994 April 2015.

- [10] k. Bhardwaj and P. S. Mane, "ACMA: Configurable Multiplication Coefficient with patient protection Chip device", in Proc. 8th. Reconstruction workshop. Centric Syst-Chip, 2013, web page. 1-6.

- [11] okay. Bhardwaj, P. Massachusetts Henkel and Mane, "Balanced, effective and effective trees, green systems for Tolerance systems" at Proc. fifteenth. conferences. electronic first-class. design (ISQED) 2014, 263-269.

- [12] JM Timeline "computer propaganda and department with binary logarithm" IRE Trans. Electrons. Comput., Vol. EC-11 number. four, p. 512-517, Aug. 1962.

- [13] V. Mahalingam and N. Ranganathan "advanced first-rate of Mitchell inside the Logarithm the usage of the evaluation of Operators," IEEE Passes. Comput., Vol. 55, no. 12, pp. 1523-1535, December 2006

- [14] Open Encyclopedia forty five Enn Gates Library to be had in 2010 [online]. available: http://www.nangate.com/

- [15] H. Auster and leather Week, this handbook Handout puzzle in Englewood picture Cliff C., New Jersey, u.s.a.: Prentice- Phnom Penh, 2009.

- [16] S. Narayanamoorthy, H. Moghaddam, Z. Liu, TN Park and Kim "effective for virtual move process Integration software" and IEEE Passing. the size integration may be very massive. (VLSI) gadget., Vol. 23, no. page 6 web page 1180-1184 June 2015.

- [17] S. Hashemi, R., I Bahar and S. Reda "Drum: An Approximate application of Dynamic range Multiplication Coefficients," in proc. IEEE / ACM Int. Conf. Calculated Calculation layout (ICCAD), Austin, Texas, usa, 2015, pages 418-425.

- [18] C.-H. Lin and i C. Lynn "particular Precision accurate trojan horse component" in Proc. thirty first. Conf. Calculate. layout (ICCD) 2013, pages 33-38.

- [19] Kahng and S. Kang "Species vectors can configure comparable strategies" at proc. 49. Conf. (DAC), June 2012, pages 820-825.

- [20] H. Wang, A. Ha Bovik, H. R. Sheikh and E Simoneelli, "photograph pleasant assessment: From shrewd feel to equal Likeness" IEEE Trans. Run the picture., Vol. 13, no. 4 pages, pages 6-6-6, April 2004 [21] J. Liang, J. Han and F. Lombardi, "New Reliability and Accreditation of Reliability signs," IEEE Trans. Comput., Vol. 62, no. web page 9, pages 1760-1771, September 2013