# Single Ended 6T Static RAM with Tri Gate FinFET in Shorted Gate Mode

Somya Sharma

MTech in Electronic and Communication Engineering. Bhagwant Institute of Technology Muzaffarnagar, UP, India

Abstract— The decision to maximize performance in terms of overall performance, power consumption, delay, leakage, and time to market (opportunity cost) has not changed since the advent of the integrated circuit (IC) industry. In fact, Moore's law is all about optimizing those parameters to their fullest potential. However, while scaling of producing nodes continued in the direction of below 32 nm, certain of the tool settings could not be scaled any further, most notably the power supply voltage, which is the primary component in determining dynamic electricity. This was the case even though scaling of producing nodes continued in the direction of below 32 nm. Through the course of this research, the power consumption, latency, and leakage currents in 6T SRAM cells are all going to be reduced. When looking at the power consumption and delay of SRAM, the backend device Synopsys HSPICE was used for the experiment. Using FINFET technology, this study builds and simulates a 6T SRAM in a 32 nm era. The size of the device is measured in nanometers.

Keywords—SRAM; 32nm; FinFET; Single Ended

### I. INTRODUCTION

The embedded memory in the portable microprocessormemory space devoted to controlled devices is a significant portion of the system-on-overall chip's storage capacity (SoC). In order for the battery in these portable gadgets to last for a longer amount of time, the circuits inside of them need to use an extremely low amount of power. It is possible to lower power consumption by, among other things, using nonconventional device designs, creative circuit topologies, and architectural optimization approaches. In spite of the fact that scaling voltage has made it feasible for circuits to function in the subthreshold zone while using the least amount of power possible, it has also resulted in an exponential decline in the devices' overall performance. RAM, or random-access memory, is a kind of data storage that is used in computing. RAM stores data as well as machine code that is currently being used by the computer. Because of this, a random-access memory device allows data objects to be read or written in roughly the same amount of time regardless of where they are physically located within the Dr. Lokesh Kumar Bansal Director, Bhagwant Group of institutions Muzaffarnagar, UP, India

memory device. This is true despite the fact that a randomaccess memory device may contain data in a variety of different locations. When using other direct-access data storage media such as magnetic tapes and drum memory, the amount of time needed to read and write data items varies significantly depending on their physical locations on the recording medium. This is because mechanical limitations such as the speed at which the media rotates and the movement of the arm make this possible. These types of media include things like hard discs, CD-RWs, DVD-RWs, and even older things like magnetic tapes and drum memory. In order to read or write an entry into the memory, the RAM has multiplexing and demultiplexing circuitry built into it. This circuitry links the data lines to the storage that is assigned for that purpose. RAM devices often consist of numerous data lines, which is why they are commonly referred to as "8-bit" or "16-bit" devices, amongst other designations. This is because the same address may usually be used to access more than one bit of storage. In today's advanced technology, random-access memory, often known as RAM, may frequently be found in the form of integrated circuits. RAM, or random-access memory, is often associated with volatile kinds of memory (such as DRAM modules), in which the information that has been stored is lost if the power is switched off. However, non-volatile RAM has also been developed. RAM is used in a variety of electronic devices. There are also other kinds of nonvolatile memory, such as those that provide random access for read operations but do not permit write operations and have various kinds of constraints placed on them. It is forbidden, for instance, to use random access for any process involving writing. The user-friendly devices that are controlled by microchips are equipped with an internal memory that is analogous to a sizeable percentage of the architecture contained on a microprocessor chip (SoC). These convenient frameworks need the use of ultralow power disbursal circuits in order to prolong the battery's useful life. It is possible that the use of nontraditional device architectures, novel circuit topologies, and technical breakthroughs will all contribute to reduce the amount of force that is used. In spite of the fact that voltage scaling has made it possible for circuits to run in sublimit administration while using the least amount of power, there is a disadvantage in the shape of an exponential

VOLUME: 06 ISSUE: 08 | AUGUST - 2022

IMPACT FACTOR: 7.185

ISSN: 2582-3930

decline in performance. The operation of the circuit inside the sub threshold administration has made it possible to build ultralow power inserted memories, which are essentially static RAMs. This was made possible as a result of the fact that the RAMs are static (SRAMs). It is conceivable that the data stability of an SRAM cell will be a considerable challenge in sub threshold administration. Furthermore, this problem will get more severe as the scaling of MOSFETs to sub nanometer technology proceeds. When using an ultralow voltage (ULV) power source, it is more challenging to figure out the ordinary 6-transistor (6T) cell due to the impediments described above. In order to make an already difficult situation even more challenging, 6T has a bad case of scan irritation. Disconnecting the real golf stroke away hub from the bit lines while the scan is being performed is an essential step in resolving this issue, as has been shown on several occasions. Doing so will eradicate the problem. The user-friendly gadgets that are controlled by microchips come with memory already installed, which represents a significant chunk of the framework on chip (SoC). In order to lengthen the battery's life span, these convenient frameworks need the use of power-wasting circuits that use an extremely tiny amount of power. It is possible to lessen the quantity of energy that is used throughout the manufacturing process by using nontraditional apparatus layouts, novel circuit topologies, and technical developments. Despite the fact that voltage scaling has made it possible for circuits to run in sublimit administration while using the least amount of power, there is a drawback in the shape of an exponential drop in performance. Because of the circuit activity in the sub threshold administration, it has been able to construct ultralow-power implanted memories that, for all intents and purposes, function as static RAMs (SRAMs). However, in sub-threshold administration, the information stability of the SRAM cell is a major worry, and it deteriorates as the scaling of MOSFETs to sub-nanometer technology develops further. This is a problem since it makes it more difficult to do sub-threshold administration. Because of these limits, it is becoming more challenging to run the normal 6-transistor (6T) cell on ultralow voltage (ULV) power sources.

SRAM is the most common kind of storage element found in nonvolatile memory, hence its name appropriately describes it as "static random-access memory." SRAM is an abbreviation for "static random access memory," which refers to a storage element that remembers and stores important data for as long as a power source is connected to its input. The dependability of the data is preserved, notwithstanding the possibility that this feature may result in an increase in the amount of power used under certain conditions. SRAM is well-known for its excellent performance and speed due to the fact that data may be accessed continuously rather than sequentially and that data refreshment is not needed. This is one of the reasons why SRAM was developed. SRAM optimization has been the focus of a substantial amount of research over the course of the last several years. This is owing to the fact that huge amounts of data

storage are often required without occupying a significant portion of the available space in the physical memory. Because of recent developments in information and communication technology, it is now much easier for an autonomous car to access the vast amounts of data that are kept on the Internet. This makes it possible for the vehicle to drive itself. A navigation system for a vehicle, much like a smartphone or a tablet PC, is able to gather a wide range of information in its pursuit of its intended purpose. As this article is being written, the types of memory that are now the most popularly utilized and can be purchased on the market include DRAM, SRAM, NVSM, FLASH, and other technologies that are analogous in nature. These memories are essential to the progress made in the semiconductor industry as a whole, and their importance cannot be overstated. This type of memory has become more widespread in recent years as a result of the increasing maturity of integrated circuits. It can now be discovered in a wide variety of electronic products, such as personal computers, mobile phones, networks, and other devices that are functionally analogous to these. SRAM is an essential component necessary for the operation of computer systems and must at all times be kept in good working order. It has become one of the most extensively used memories in the world due to its small size, tremendous capacity, quick speed, and high resilience. [This is] because of its tiny size, enormous capacity, rapid speed, and high durability. Information is saved in SRAM primarily via the use of two inverters that are cross-coupled with one another. The data will always be retained on the hard drive so long as the power supply is kept operating continuously without interruption.

SRAM, which stands for "Static Random Access Memory," is a sort of semiconductor memory in which each bit is stored by means of bi-stable latching circuitry, which is a type of bistable latching circuitry. As its name suggests, SRAM is a form of random-access memory that is static (flip-flops). Even if it demonstrates data persistence, it is still classified as generally volatile since the data stored in it is at danger of being lost whenever the device in question is turned off. This is the case even if it does display data persistence. In addition to functioning as cache memory for the central processing unit (CPU) and DRAM (Dynamic Random Access Memory), it was developed with the intention of being utilized to replace DRAMs in low-power computer systems. When it comes to the responsibility of storing information, one of the most important functions that an SRAM cell must be able to do is to be able to store a single bit of data. It is possible for an SRAM cell to carry out this function if it satisfies the static conditions for the data stability. The Static Noise Margin, often known as SNM, is a well-established statistic that is used for evaluating the consistency of data in the area of data stability. If a certain amount of direct current noise, also known as DC noise, is introduced into a cell, then that cell will no longer be able to satisfy the static criterion for data stability. This is what is meant

VOLUME: 06 ISSUE: 08 | AUGUST - 2022

IMPACT FACTOR: 7.185

ISSN: 2582-3930

by the term SNM. Microseconds are used to measure the amount of time that elapses between two SNMs. Throughout the design process, one of the most important considerations to give attention to is the SRAM cell's level of stability. Because the memory cells are so stable, it is possible to anticipate in advance how sensitive the memory will be to the operating circumstances and the tolerances of the processing. It is necessary that it be able to keep working properly even when there are noise signals present or other types of disruptions. An SRAM cell's direct current noise margin is a measurement of how stable the cell is while operating in an environment where there is direct current noise (DC) (SNM). The amount of voltage noise that must exist at the cell's output nodes for the cell to change its state is represented by the symbol SNM. This noise must exist at each of the cell's output nodes. Examining the voltage transfer characteristic (VTC) of the SRAM cell's two cross-coupled inverters is one way to find out this information. Because of the growing need for the capacity to store vast quantities of data, fabrication technology has evolved in recent years. According to Moore's law, the number of transistors that can be integrated into a single chip will double every two years, which is a substantial increase. In this particular setting, the development of high-performance memory circuits that are compatible with the system-on-chip technology of the present day is absolutely necessary. Memory's primary roles include not just the capacity to store information but also to read, write, and access information that has been previously stored. Memory may either be volatile or nonvolatile, and both types are accessible to users. Volatile memory is the more common kind.

According to experts in the industry, the demand for batterypowered appliances such as laptop computers, cellular phones, and other portable communication devices continues to rise at a startling rate on a daily basis. Examples include portable communication devices. This trend is anticipated to continue as the dimensions of MOSFETs continue to be shrunk with each new generation of technology in order to achieve high performance and high integration density in SRAMs and other memory devices. The static power dissipation finally becomes a serious concern since it develops exponentially in direct proportion to the increase in threshold voltage. Because cache occupies a considerable amount of space on a System-on-Chip (SoC), one of the most important requirements in low-power design, particularly for flash memory, is the reduction of leakage power in SRAM memory. This is done in order to bring down the overall amount of power that is consumed. The storing of data for a brief period of time may be done using a kind of random-access memory known as SRAM. The acronym DRAM stands for dynamic random access memory, and it and flash memory are not interchangeable in any way. SRAM must be able to interact directly with the CPU at rates that are not attainable with DRAMs, and it must be able to replace DRAMs in systems that require extremely low power consumption in

order for it to be effective. These are the two essential conditions that must be met in order for SRAM to be effective. SRAM operates at a quicker speed as compared to DRAM, which enables operations to be carried out in a more effective manner. The quicker access to the data is a direct outcome of this innovation, which was implemented as a consequence of this improvement. It is used to generate a cache that is responsive to variations in speed and only requires a little amount of power throughout the process. In this research, work is done on SRAM devices that have a single ended structure and whose performance is increased utilizing FinFET.

### II. LITERATURE REVIEW

Nanometer method technologies have progressed as a result of Because of this innovation, chip density and operating frequency have grown, which has resulted in a significant increase in the amount of energy that is used by batteryoperated portable devices. Even if there were no portable devices, there would still be a substantial amount of power consumption owing to the increasing expenses of packing and cooling, as well as the issues associated with the reliability of the ability. As a consequence of this, achieving overall performance requirements while staying within power budget limits is the fundamental design aim for VLSI (very large-scale integration) designers. [3] Scaling of gate MOSFETs in nm confronts an especially tough assignment as a result of the extreme short channel effect. As a direct consequence of this, an exponential increase in sub-threshold and gate-oxide leakage, in addition to DIBL [1], may be seen. This is due, in part, to the fact that the method of producing FINFET and MOSFET are essentially similar [2], which makes them a potential option for bulk MOS at the nanoscale. FinFETs (fintype double-gate field-effect transistors) [4] offer an intriguing strength-delay tradeoff in addition to higher characteristics (short channel effect) in the nanometer range. This enables them to meet the overall performance expectations that have been outlined in the global technology roadmap for semiconductors for the technological node that is rapidly approaching. [5].

The fin-shaped metal oxide semiconductor field effect transistor (FinFET) is a kind of major steel oxide semiconductor field effect transistor (MOSFET) that has an impact on MOSFET. The pioneering work in this area was done by Chinning Hu and his colleagues at the University of Berkeley in Berkeley, California. They were the first to make major headway in this subject. The NMOS in CMOS technology is replaced with an N-FinFET in FinFET technology, and the PMOS in CMOS technology. Both gates of the FinFET are then connected together. By using this method, we will be able to create a FinFET model of a CMOS common sense circuit or a

VOLUME: 06 ISSUE: 08 | AUGUST - 2022 IMPACT FACTOR: 7.185 ISSN: 2582-3930

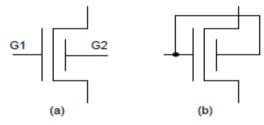

bypass transistor good judgement circuit that is capable of preserving each and every one of the characteristics that are associated with the MOSFET variation [7]. [6] FinFET is able to efficiently suppress the quick-channel effect and provide near-best sub-threshold swing [9] during the interim period, which both contribute to an improvement in circuit performance and a reduction in leakage during this time period. The rapid channel effects of the device when it is operating in the i-gate mode (threshold voltage roll-off, sub threshold swing deterioration, and drain prompted barrier reduction) are significantly less severe than the rapid channel effects of the device when it is operating in the double-gate style [2]. The FinFET Device is shown in two alternative configurations in Figure 1.

Fig. 1 FinFET (a) DGFET (b) SGFET [4]

### III. PROPOSED WORK

Using 32nm technology, MOSFETs and FinFETs are used in the construction of an SRAM cell that has a capacity of 6T, is constructed of base paper [1,] and has a structure that is single ended. The application known as Synopsys HSPICE was the one that was used. The programmed does not have compatibility with radiationhardened devices, and the code simulates the circuit on FinFET transistors, which will be compared to MOSFET transistors for applications pertaining to the aerospace industry. The proposed method will be created as a consequence of the design process for the circuit, which will use a low-power design approach that is suitable for the circuit.

The majority of digital devices that are based on microprocessors need the usage of static random-access memory, often known as SRAM. This memory is an essential part of the device. Because the technology node is getting outdated and the supply voltage is becoming less reliable, it is imperative that the performance of the technology node be upgraded. It is essential for embedded systems that are designed for portable applications with a short duty cycle, such as mobile phones and personal digital assistants, to use as little energy as is humanly practical (PDAs). Due to the fact that these gadgets are powered by batteries, it is essential that they use as little electricity as possible. Memory accesses in such systems use a substantial amount of power, which has a major influence on the total lifespan and performance of the battery. This is because memory accesses take place in such systems. Therefore, in order to lengthen the amount of time that battery-powered applications may remain operational for, it is necessary to do research on efficient active and leaky power-saving SRAM architectures. [2] This section will describe the two key areas-active power savings and leaky power savings-where there is a significant possibility for cutting power consumption and saving money. This is achieved by reducing the operating voltage to a lower level and reducing the discharging capacitance of the word and bit lines to the same level. Both of these changes bring the capacitance of the word and bit lines to the same level. It has been stated that the dissipation and charging of bit lines account for up to a third of the total active power dissipation that occurs during read and write operations [3]. [Citation needed] As a direct result of this, lowering the charging capacitance has the potential to save a significant quantity of electrical energy.

### IV. RESULTS

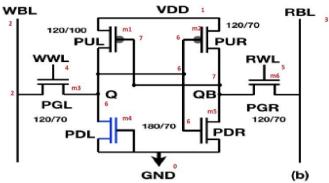

The implemented circuit is shown in figure 2 which may be seen below. It is an SRAM with a single ending. We have succeeded in producing approximate memory from a singleended SRAM cell, which we have referred to as the single ended 6-T (SE6T) SRAM cell. This achievement marks a first for our team. [10] The bulk of the power that is available is used up by the process of charging and discharging the bit-lines that make up SRAM memory. Because our proposed SE6T SRAM cell only uses a single bit-line for writing and a single bit-line for reading, it utilizes just half of the power required by a conventional 6-T SRAM cell and only consumes one-half of the power required by a standard 6-T SRAM cell. In point of fact, as compared to standard 6-T SRAM 1KB memory, the SE6T cell utilizes approximately half the power for the same amount of storage space while maintaining the same BER values as the standard memory.

In accordance with what is suggested in [4], we propose making use of heterogeneous SRAM arrays for the embedded memory of programmed that deal with multimedia data. These arrays are built using bit cells that range in size from very small to very large. In contrast to the conventional 6-T SRAM cell, in which the sizes of all of the transistors need to be increased proportionally in order to achieve the same result, the proposed SE6T SRAM cell only needs to have one of its transistors' sizes increased in order to achieve a reduction in the bit error rate (BER). This is one of the most notable advantages of the proposed SE6T SRAM cell. As a consequence of this, the MSB

Volume: 06 Issue: 08 | August - 2022

IMPACT FACTOR: 7.185

ISSN: 2582-3930

bits of a pixel are subject to a space penalty that is noticeably less severe than the LSB bits, in contrast to [4].

Fig. 2 SRAM single ended structure

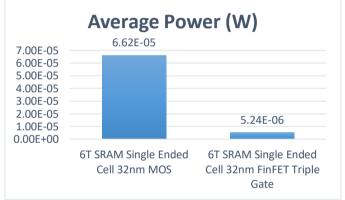

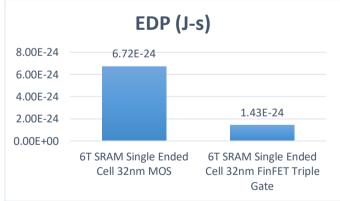

The findings are shown in figures 3 through 6. The findings presented here demonstrate that a FinFET-based single-ended structure performs more effectively than a MOSFET-based one.

Fig. 3 Average Power Comparison

Fig. 4 EDP Comparison

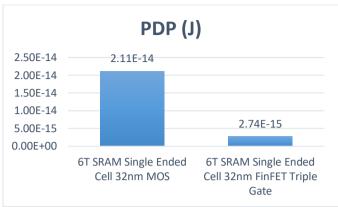

Fig. 5 PDP Comparison

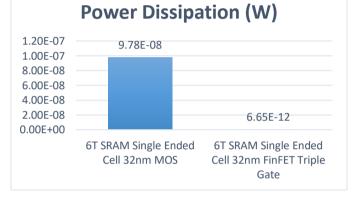

Fig. 6 Power Dissipation Comparison

## V. CONCLUSION

Despite advances in technology, the decision that has been made since the beginning of the integrated circuit business to maximize the performance metrics of overall performance, power, delay, leakage, and time to market (opportunity cost) has not changed. This decision has been made to maximize these metrics. In point of fact, Moore's law is focused on increasing the value of those characteristic

4EEWEWs as much as possible. The scaling of production nodes, nevertheless, continued in the direction of 32 nm; however, essential tool settings were unable to be scaled any further. This was especially true for the power supply voltage, which is the single most significant factor in producing dynamic electricity. The study being conducted has as its primary objective the attainment of the lowest possible levels of power consumption, latency, and

VOLUME: 06 ISSUE: 08 | AUGUST - 2022

IMPACT FACTOR: 7.185

**ISSN: 2582-3930**

leakage currents in a 6T SRAM cell. It has been decided to use the backend device known as Synopsys HSPICE for the purpose of researching the power consumption and latency of SRAM. The development and simulation of a 6T SRAM in the 32 nm timeframe is shown in this work. This was accomplished via the use of FINFET technology. The findings indicate improved functionality in the work that was recommended.

#### REFERENCES

- N. Surana and J. Mekie, "Energy Efficient Single-Ended 6-T SRAM for Multimedia Applications," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 6, pp. 1023-1027, June 2019, doi: 10.1109/TCSII.2018.2869945.

- [2] A. Mishra and A. Grover, "A 0.9V 64Mb 6T SRAM cell with Read and Write assist schemes in 65nm LSTP technology," 2020 24th International Symposium on VLSI Design and Test (VDAT), 2020, pp. 1-4, doi: 10.1109/VDAT50263.2020.9190373.

- [3] A. Mishra and A. Grover, "A 0.9V 64Mb 6T SRAM cell with Read and Write assist schemes in 65nm LSTP technology," 2020 24th International Symposium on VLSI Design and Test (VDAT), 2020, pp. 1-4, doi: 10.1109/VDAT50263.2020.9190373.

- [4] R. R. Vallabhuni, P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [5] P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [6] Mahender Veshala , IJEIT 2013, "Reduction of Short-Channel Effects in FinFET"

- [7] V Narendar, IJCA, 2012, "Design of High-performance Digital Logic Circuits based on FinFET Technology"

- [8] PC Rajashree, ICIET-2014, "Deep Submicron 50nm CMOS Logic Design with FINFET"

- [9] Tushar Surwadkar, IJETT-2014, "Upgrading the performance of VLSI Circuits using FinFETs"

- [10] Chunyu Peng, Jiati Huang, Changyong Liu, Qiang Zhao, Songsong Xiao, Xiulong W, "Radiation-Hardened 6T SRAM Bitcell With Speedand Power Optimized for Space Application", IEEE, 2018

- [11] S. S.R., B. R. S., Samiksha, R. Banu and P. Shubham, "Design and Performance Analysis of 6T SRAM Cell in 22nm CMOS and FINFET Technology Nodes," 2017 International Conference on Recent Advances in Electronics and Communication Technology (ICRAECT), 2017, pp. 38-42, doi: 10.1109/ICRAECT.2017.65.

- [12] U. Mushtaq and V. K. Sharma, "Design of 6T FinFET SRAM cell at 7nm," 2019 International Conference on Communication and Electronics Systems (ICCES), 2019, pp. 104-108, doi: 10.1109/ICCES45898.2019.9002138.

- [13] Y. Ma, L. Zhang and J. Liu, "A New 6T SRAM Memory Cell Based on FINFET Process," 2020 IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM), 2020, pp. 251-254, doi: 10.1109/ICICM50929.2020.9292226.

- [14] R. R. Vallabhuni, P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [15] Rath, Subhashree & Panda, Siba. (2017). Analysis of 6T SRAM Cell in Different Technologies. Circulation in Computer Science. MCSP2017. 7-10. 10.22632/ccs-2017-mcsp026.

- [16] Devi, Meenakshi & Madhu, Charu & Garg, Nidhi. (2020). Design and analysis of CMOS based 6T SRAM cell at different technology nodes. Materials Today: Proceedings. 28. 10.1016/j.matpr.2020.05.130.

- [17] Ezeogu, Apollos. (2019). Performance Analysis of 6T and 9T SRAM.

- [18] Hansraj, A. Chaudhary and A. Rana, "Ultra Low power SRAM Cell for High Speed Applications using 90nm CMOS Technology," 2020 8th International Conference on Reliability, Infocom Technologies and Optimization (Trends and Future Directions) (ICRITO), 2020, pp. 1107-1109, doi: 10.1109/ICRITO48877.2020.9197869.

- [19] A. S. V. S. V. P. D. Kumar, B. S. Suman, C. A. Sarkar and D. V. Kushwaha, "Stability and Performance Analysis of Low Power 6T SRAM Cell and Memristor Based SRAM Cell using 45NM CMOS Technology," 2018 International Conference on Recent Innovations in Electrical, Electronics & Communication Engineering (ICRIEECE), 2018, pp. 2218-2222, doi: 10.1109/ICRIEECE44171.2018.9009119.

- [20] B. Satheesh and P. Benakop, "Design of an AAM 6T-SRAM Cell Variation in the Supply Voltage for Low Power Dissipation and High Speed Applications using 20nm Finfet Technology," 2020 International Conference on Inventive Computation Technologies (ICICT), 2020, pp. 1080-1086, doi: 10.1109/ICICT48043.2020.9112590.